- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA Runtime Version Register

03-01-2013 01:59 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Is there a way to get a version number or compile timestamp of a LabVIEW FPGA bitstream from within the FPGA while running? I would like to be able to have a build number embedded in the FPGA so when it's running it can report the compile version without resorting to manually populating a control, global, BRAM, etc.

Not being a heavy LabVIEW scripting user, does anyone know if a compile can be kicked off within a script? This would let the script update the source with a version and then build it in one step.

What would be great is a VI in the the NI libraries that replies with a U32/U64 based on the compile time in seconds (like the time/date to seconds function in Windows). Then no extra steps are needed to embed the data.

Any ideas?

03-04-2013 06:41 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi tkreider,

If I'm understanding your question correctly, you could use the File I/O functions (Open/Create/Replace File, Read from Text File, Match Regular Expression) to parse the bitfile for the Bitfile version.

I'll continue looking into kicking off a compilation with a script.

Applications Engineer

National Instruments

03-04-2013 07:05 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks Dave. While this solution works within LabVIEW for Windows, those features (Open/Create/etc) are not available within the LabVIEW FPGA target scope. I tried making an initializer VI for a VI Scoped memory within LV FPGA which returns a timestamp (2 U32's with the initializers run-time in seconds using Time in Seconds). Unfortunately, the initializer isn't called at compile time automatically, it must be run by hand before starting the top-level compile.

What I would like is a way to have that initializer run for me at top-level compilation time automatically. If there is some way to read it from within LV FPGA without creating my own hack (memory) that would be great. Say maybe, a block that reads a timestamp from the Xilinx bitstream in flash... 🙂

Thom

03-05-2013 08:18 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Thom,

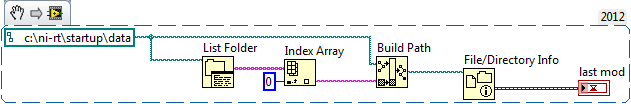

In consulting with colleagues, we haven't identified a way to do it on the FPGA. It has to be determined from the host because that is where the bitfile resides (real-time, Windows, etc.). The idea is to browse the bitfiles in a specified directory and look at the last updated time. This will give you the time of when it was built or deployed (depending on OS). Keep in mind that it will only work if it's set as the startup application on the real-time target.

Applications Engineer

National Instruments

03-06-2013 10:10 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dave,

Thanks for taking up the cause. Let's supposed that the FPGA bitstream is deployed to the hardware target to start on power-up without a controller yet running. The bitstream is parked in flash and without anything else running, I'd like to know the timestamp of the build that is running.

Thom

03-07-2013 07:46 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Thom,

Still working on this... The thought is to parse the bitfile and write the version to a register or memory on the FPGA. FPGA does not support the timestamp data type.

Could you provide me some of the bigger picture? Why do you want the timestamp or version number and how will you use it once you have it?

Applications Engineer

National Instruments

03-08-2013 08:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

This sounds like a good feature request for the FPGA Idea Exchange. The Build Specifications already have the notion of a version, so one very simple request would be to include that version number in the compiled image of the device (it currently just resides in the LabVIEW FPGA bitfile, not in the image for the actual hardware). A step further would be a register with the actual compile time, but there you get into timezone and other issues.

03-08-2013 09:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dave,

I have an application where the FPGA has several communications links to the outside world. Over those links, we would like to be able to query the FPGA as to the revision number of the running IP. Having the FPGA report its revision number based on information given to it from another device (with a different revision number) isn't the most reliable mechanism.

Having something like a timestamp embedded in the FPGA that can be trusted would be ideal. Having to update the register manually before compilation leaves the process open to a high-probability error on the operators part. Having an external entity inform the FPGA as to the FPGA IP revision number is also ripe to several more failure modes.

It seems like this should be added to the FPGA feature request page as suggested. While I have access from the FPGA at runtime to the raw bitstream file in Flash, staying inside the toolchain and having LV reporting the data would be ideal and applicable to the larger LV user community.

Thom

03-11-2013 09:01 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Thom,

If you're not familiar with the FPGA Idea Exchange, you can click here.

Applications Engineer

National Instruments

03-11-2013 01:06 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dave,

So it sounds like we've run out of options on getting LV support for the version register within the existing tool? I'll post to the Idea Exchange if we agree we exhausted our options.

Thanks for your help!

Thom