- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »

FPGA, RT and cRIO

01-16-2019 02:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I strongly doubt that you achieve a sample rate of 1 MS/s with this design.

As stated in this KB the maximum sample rate for a 9223 module using the I/O node is 350 kS/s.

There is a very good example in the NI example finder of how to use the 9223 with 1 MS/s. Just search for 9223 and open the project "NI 9223 User-Controlled IO Sampling.lvproj".

Regards, Jens

01-16-2019 08:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi GerdW

Thank you very much for the info. This is my first time using FPGA, RT, FIFO please bare with me.

I made all the changes that you suggested but I am still getting the same error.

Attached find ZIp file for the project (please note: RT application = RT_b and FPGA application = FPGA_b)

In FPGA_b

I am still trying to understand how to design a case structure to execute based on rising edge of the the TTL but not sure what input from Mod1/DIO4 (in the software) should be fed into it

Thanks again.

Best regards

01-16-2019 03:57 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Jay,

Are you trying to achieve something similar to what is being done in this example program?

01-17-2019 07:53 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

It is different from what I want

Thank you

01-21-2019 03:53 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Jen,

This solution seems to work except one issue. Yes 9223 acquire data at 1 MS/s rate. However, RT application takes 38 ms to run which slows down data acquisition for my next trigger signal. Is there any suggestion to spped time for RT loop to 2 ms because the time difference between consecutive trigger signals is 2 ms

Appreciate your help!

01-22-2019 06:57 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@JayanthaS wrote:

This solution seems to work except one issue.

What solution are you referring to? You didn't attach anything. Or should we be looking at your previous posting of your code?

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

01-22-2019 11:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I am following Jen's ussgesion here.

I am using "NI 9223 User-Controlled IO Sampling.lvproj" example to acquire data in rate of 1 MS/s. Using the RT application (in this example) I can get 1000 sample in 1 ms - This great. However I want to proceed this ~ every 2 ms (when ever I receive a trigger signal). The bottleneck is execution time for above RT is 38 ms therefore I cannot start the data collection for my next trigger signal on time. Is there a way to reduce the execution time for above RT application in the example. One though is do I need to run "open fpga vi reference" each time RT application starts

Hope you could help with this

Thanks.

Jayantha

01-22-2019 01:06 PM - edited 01-22-2019 01:21 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

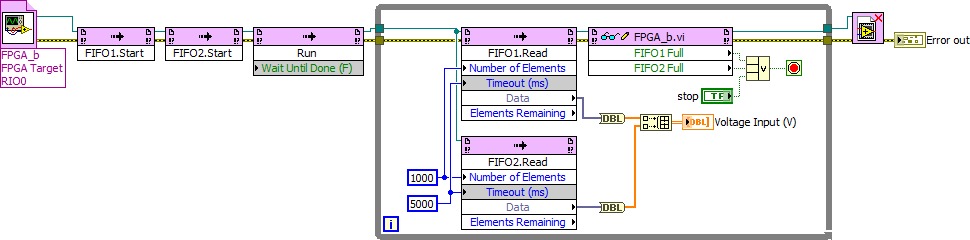

Hi Jayantha,

do I need to run "open fpga vi reference" each time RT application starts

Yes - as you need the FPGA reference to enable communication with your FPGA…

What about this:

Read the FIFOs in parallel, and read the FIFO states with just one node…

Btw. all your FPGA VIs contain quite senseless code: why do you stop the FPGA basic routine after putting just 1000 samples into the FIFO? Usually the FPGA code will run forever!

- « Previous

-

- 1

- 2

- Next »