- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA- Producer loop rate increases with number of analog output placed in parallel loops.

Solved!11-03-2020 09:32 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

Hope you are doing good and thank you for taking some time out for reading the post.

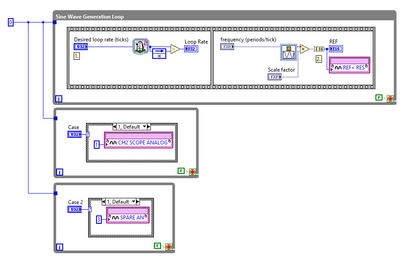

Scenario: I have a main loop (Producer) that generates ref sine wave. In parallel, I have two loops that captures sine/cosine (respectively) coming back from resolver which will be simply passed through analog output channel.

(Analog input [Raw format]----connects directly to------Analog output [Raw format])

I have refactored the code (attached image and VI) for simplicity to just show the slowing down part. Also, everything works as expected in simulation mode.

Problem Statement: Even by placing analog output blocks in parallel loops, the main (producer) loop slows down by:

1) One analog output block on diagram: 141 ticks (not a problem)

2) Two analog output block on diagram: 252 ticks (problem)

3) Three analog output block on diagram: 378 ticks (major problem)

(1 tick = 25 ns)

It seems like I am missing out something fundamental here. I did try out different scenarios but they all resulted the same. I would really appreciate if someone could guide me in the right direction..

-Thanking you

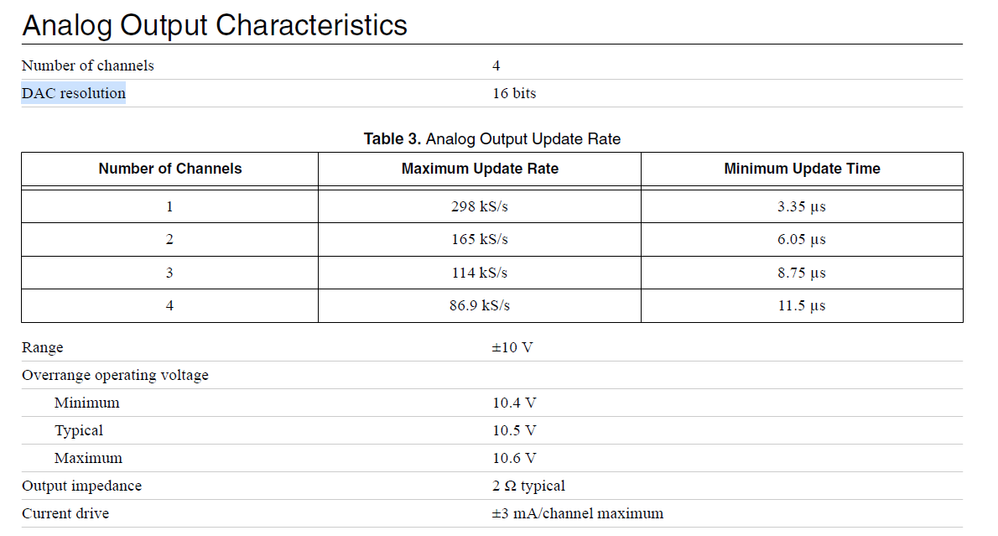

Additional Information: Could the update rate be affecting the loop rate?

Solved! Go to Solution.

11-03-2020 10:09 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

11-03-2020 10:30 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi GerdW,

I really appreciate you responding.

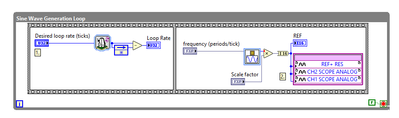

I did put in all the AO in one loop and in one IO node as suggested. But the loop rate is still high, it is 354 ticks. I need it to be around 141 ticks.

Do you have any other recommendation? Also is increased tick count inevitable with increased AO?

Thanking you

11-03-2020 12:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

What I should have written is that; I put all the AO nodes in separate loops thinking that if I processes these blocks in parallel on FPGA the loop rate will remain low for all the loops.

I get the best results when the sine wave producer loops runs at 141 ticks or less.

If there is no way to meet both the requirements, I will avoid using more than one AO node in the single code.

11-03-2020 03:50 PM - edited 11-03-2020 03:54 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Xonmyth,

@XM43 wrote:

But the loop rate is still high, it is 354 ticks. I need it to be around 141 ticks.

Do you have any other recommendation?

So it became faster than before by ~20 ticks!?

According to the specs the update time for 3 channels is 8.75us: 350 ticks * 25ns/tick = 8750ns =8.75us.

What else did you expect?

On "parallel access" on FPGA: on cRIO the modules are connected to FPGA using a serial bus. This bus is a shared resource! Using more channels can lead to reduced sample rates per channel.

I guess the sbRIO behaves very similar...

11-03-2020 05:22 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi GerdW,

Pardon my lack of knowledge. This is what I suspected but I was not sure of.

Thank you.