- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA Phase-Offset

07-06-2021 10:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello!

I work with the following hardware:

cRio 9054 Chassi

S-Series 9269 Analog Output Module

The cRio should work as a signal generator. Three signals are to be generated with a phase offset of 120 degrees each.

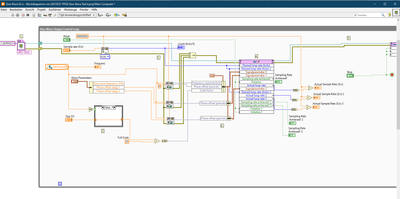

The signal frequency is increased with a fixed iterations f={1Hz, 2Hz, .... 20kHz}. I generate the signals on the FPGA with the Sine Wave.VI.

The signal parameters are transferred via the Host.Vi (frequency, phase offset, amplitude). The 3 generated signals are output from the FPGA.

Now to the problem:

The phase offset of the signals varies. It does not remain constant at 120 degrees. I suspect that the problem lies in the parallel generation of the 3 signals. I am relatively new to programming on an FPGA and am not very familiar with timing problems. My first try was to seperate the generation functions in seperate loops. Is there a way to regulate the phase shift on the FPGA? Or how can the parallel processing be better utilized?

Many Thanks for Your help!

07-06-2021 12:05 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator