- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA Matrix multiplication - Linear Algebra Matrix Multiply

Solved!11-01-2020 09:52 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

All

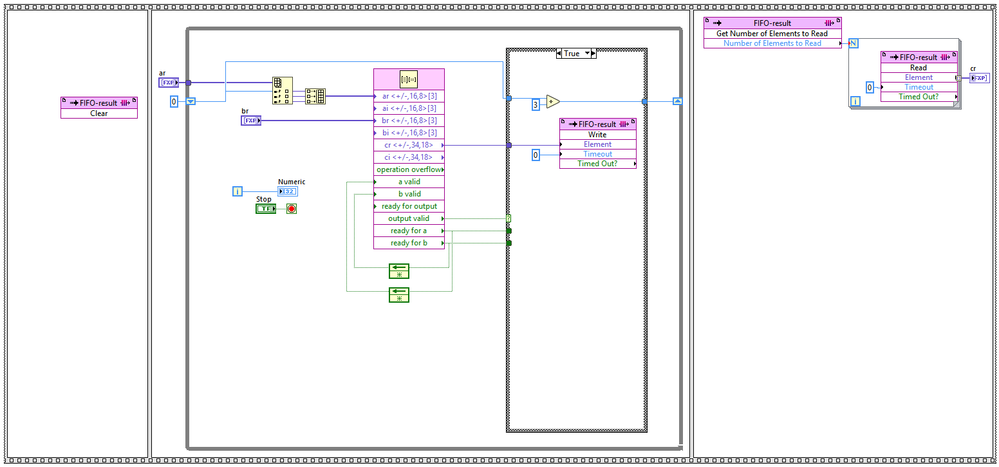

I am trying out the matrix multiplication via Linear Algebra Matrix Multiply. Attaching the project where you should see the T_PZ.vi.All I am trying to do is to understand how this works. When I use the VI in FPGA simulation mode, I see weird results - not wrong but repeated numbers out of which a subset is the correct answer.

I don't see very many examples on web either. Anybody?

Solved! Go to Solution.

11-02-2020 09:12 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I would switch the FIFO Write Interface to use Handshaking (it is set to Timeout). You can then use its output to handshake with the matrix function and remove the case structure.

Timeout is not used as much any more (though it is still the default setting). That reminds me to put that request into the Idea Exchange.

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

11-02-2020 02:25 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

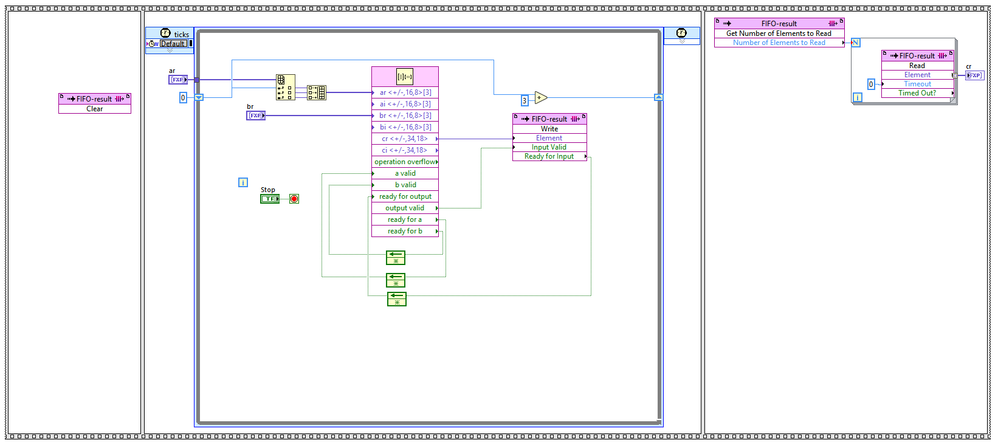

Thank you for your reply. Something like this?

11-02-2020

03:54 PM

- last edited on

01-20-2026

11:56 AM

by

![]() Content Cleaner

Content Cleaner

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

That's better. Next would be to switch the Read FIFO to handshaking mode and read only when Output Valid is true.

Get number of elements to read is not being used correctly (see https://www.ni.com/docs/en-US/bundle/lvfpga-api-ref/page/vi-lib/rvi/fifo/fifo-common/get-number-of-e...). If you use the handshaking, you do not need this function. What do you want to do with the data afterwards?

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

11-02-2020 04:44 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

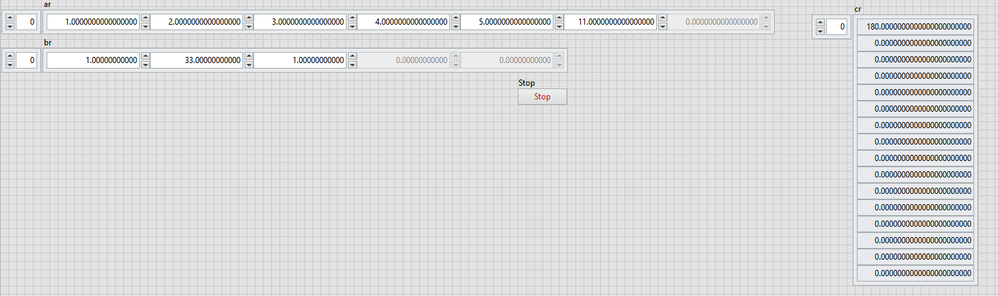

I tried that its the same results as previous effort. But a noob question - wouldn't the extra elements point to me writing to FIFO when I shouldn't be writing?

It almost seems like output valid is high for multiple cycles after i get the first valid output and it spews the same redundant result - confused as to why that will happen?

11-03-2020

06:03 AM

- last edited on

01-20-2026

11:56 AM

by

![]() Content Cleaner

Content Cleaner

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

That's because a valid and b valid keep getting true values coming in.

Check out https://www.ni.com/docs/en-US/bundle/labview-fpga-module/page/scheduling-timing-using-handshaking-si... to see more on how handshaking works in a more generic example. The issue you are facing is not specific to the matrix function.

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

11-03-2020 11:19 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you!

I do understand the idea behind a and b being valid.

But outside of ready for a and ready for b I am not sure what other knobs I have to wire back?

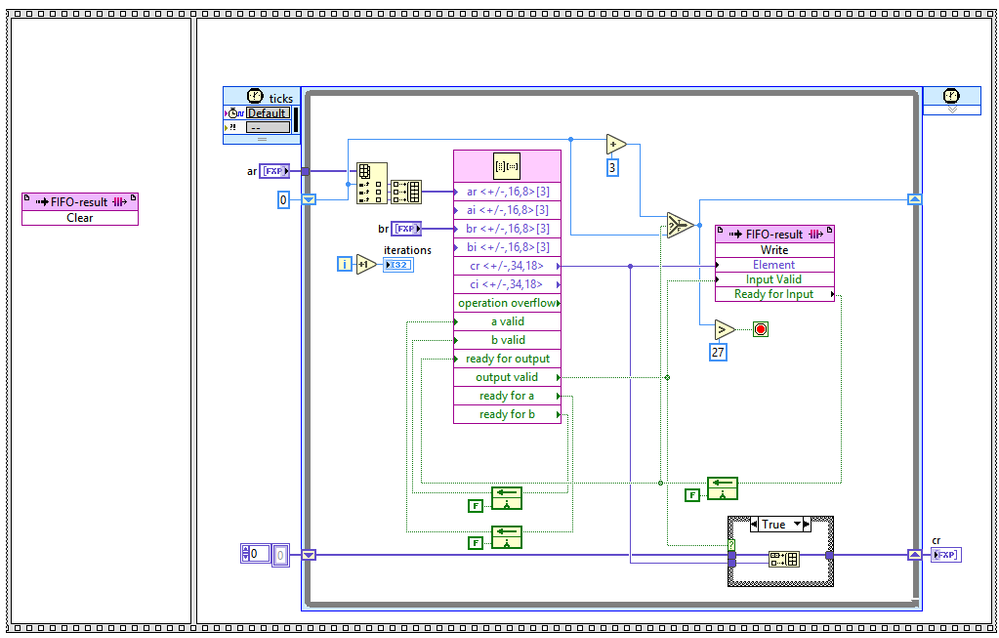

I tried this, and it seems to work.

11-03-2020 03:03 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

It doesn't make sense to wire "ready for a" into "a valid."

Ready for a (or b) gets wired back to the source, the function before the multiply. Do you know what will replace the control?

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

11-03-2020 03:28 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

It'll be very similar to what i have on here. It'll be a matrix. In this case, I want to pass 2 vectors which grouped together constitute a matrix.

12-10-2020 08:59 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator