- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA FIFO to Serial on cRIO

01-18-2022 09:25 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

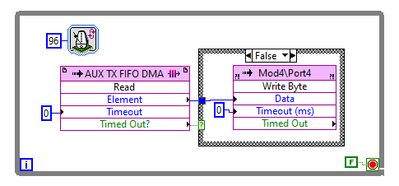

I have the following code

The intended functionality is fairly self explainatory but just to be as clear as possible, Bytes in the FIFO (set up as U8) are read one at a time and sent to one of the the serial ports on a NI-9871 (Mod4\Port4). This is done every 96uS to insure there is no data collision at 115200 baud as I do not know if this is automatically handled and the timeout is used to detect an empty FIFO (the true statement in the case structure dows nothing). A timeout of 0 on the fifo has also been tried, to make the while loop wait until there are bytes available in the FIFO. In the RTOS, a string is turned into an array of ASCII values and sent to the FIFO. I would expect to see that string appear at the serial port.

What I am actually getting at the serial port is the first character placed in the FIFO repeated indefinitely. The vi in the RTOS has been checked and is definitely placing the correct data in the FIFO so the issue has to be with the above. It would appear that the FIFO is failing to advance each time a byte is read and placed on the serial port. Does anyone know how to fix this?

01-18-2022 11:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

What I would do is replace the 9871 I/O block and use some array functions to do a quick 'sanity' check whether each iteration is reading the byte from FIFO. If it fails here, there's something wrong with the FIFO configuration.

01-18-2022 12:02 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi, thanks for the reply

I've done something similar to that. There's a second FIFO to read data back from the 9871 I/O. If I connect the two FIFOs together then data goes from the RTOS to the FPGA throught the first FIFO and is returned through the second FIFO. Everything works fine until the 9871 I/O blocks are introduced.

01-18-2022 12:33 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Ok. Let us take a little step back.

The NI-9871 is a RS422/485 serial module. The RS422 standard says the following:

1. Header (2 bytes)

2. Body (8 bytes)

3. CRC (2 bytes)

Total (12 bytes)

Now we assume that the header and CRC are incorporated by the 9871 FPGA IP itself and we only need to send the body (8-bytes). The baudrate you have set is 115200, which, correct me if I am wrong, means 115200 bits/sec which means that the entire chunk (or frame) is getting pushed at 14,400 frames/sec.

Now, you're timer of 96us means each byte is being written at this rate which means for 8 bytes (body only), it will take 768us. Is this rate fast or slow, according to the RS422 standard and your baud rate setting?

01-18-2022 12:36 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I think I am wrong. Let me formulate this once again.

01-18-2022 02:40 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You should monitor the Timeout output from the Write FIFO. If that is true when you try to write, then data is being dropped/lost.

The 987x shipping example shows how this should be done.

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications