- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA DMA FIFO, Communication Error

Solved!07-27-2021 07:45 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

I am working with an PXI-7851R, and I am having a problem that I would like some help with solving. The problem occurs on a new computer running windows 10, which has a PCIe-8361 inside it. This connects to a PXIe-8360 controller housed in the chassis with the FPGA module. I am currently using labview 2015 SP1.

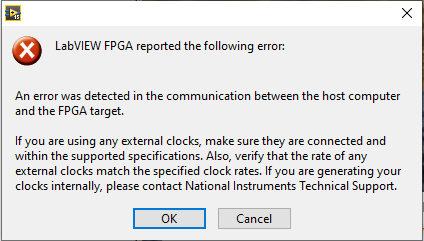

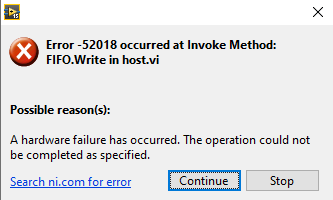

Although compiling, loading a bitfile to the FPGA and running it, front panel FPGA communication, etc, is working without issue, I am having a communication error when I try to use a DMA FIFO to stream data from the host to the fpga target. Basically the data is not able to be read from the FPGA side due to the communication error. I believe that this is not a coding problem, as the same problem occurs when using the DMA streaming example that comes with labview. Additionally, when I switch the PCIe-8361 card to a different computer, the FIFO runs as expected without error using the same code.

Here is the error I have been getting:

I have tried updating all software version, drivers and firmware for the NI hardware, as well as updating the computer BIOS to the latest version (which solved a similar problem for some people), but the problem still persists. Does anybody have any idea how to solve this problem, or what may be the root cause? I'd appreciate some guidance.

Regards,

Jonathan

Solved! Go to Solution.

07-27-2021 02:13 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

When you mention "front panel FPGA communication" are you directly running the FPGA VI from the computer?

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

07-27-2021 07:51 PM - edited 07-27-2021 08:19 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Yes, for example, if I create an FPGA targeted VI that has a control or indicator on the front of the VI, I can run that VI from the computer, and the controls and indicators work as expected (e.g. controlling the analog I/O on the PXI-7851R module)

However, when I attempt to programatically open a reference to an FPGA VI and write to the host-to-target DMA FIFO, the FIFO reports 0 elements remaining, and I receive the errors mentioned above. Additionally, the host VI freezes and I have to restart the computer, since I cannot stop the host VI. Here, the whole computer is not frozen, just the host VI is stuck in an endless loop of attempting to reset.

Hopefully this sheds more light on my problem so that somebody may be able to help. If anybody has an idea for what to try in order to troubleshoot this problem, please let me know. I'll attempt to work on this more today...

07-28-2021 02:31 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

After working on this problem again today, I think that the issue is now solved.

It seems that it was a BIOS issue, meaning that the PCIe-8361 card was not able to function correctly. By installing the "MXI-Express BIOS compatibility" software from NI, and setting the BIOS compatibility mode DIP switch on the PCIe-8361 to ON, my FIFOs now function as expected.

07-28-2021

09:24 AM

- last edited on

01-14-2026

03:48 PM

by

![]() Content Cleaner

Content Cleaner

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Seems like you are using Interactive mode (https://www.ni.com/docs/en-US/bundle/labview-fpga-module/page/interactive-front-panel-communication-...).

I find this to be quite limiting. Though it can be good for spot checking it is best to programmatically open the FPGA VI and interact with it that way.

Looks like it was a BIOS issue. Never saw that before but good that it has been figured out.

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications