- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA Analog input to Output delay

11-18-2020 01:03 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

I am using a cRio 9030 (4 slots) target with two AI modules (NI 9239) and an analog output module (NI 9264) to implement a discrete PID control algorithm for a custom plant. I use the AO module as the actuators of the plant receive such output voltages and convert them to the desired currents. I am using the FPGA because the loop rate of the system has to remain below 130 us.

Aiming to assess the FPGA loop behavior, a VI for the FPGA and the Host (RT target) was created in a Labview project. The sample rate of the acquisition was determined as 10kHz (below the maximum rate -50kHz- for AI modules and -25kS/s- for AO module) and the two NI 9234 are synchronized with a master module clock, as presented in the NI 923x examples. When the VI is run, the target reads the AI modules channels and then writes the same data in the AO module. The acquired data from AI modules are stored in a FIFO and read by a FIFO item in a parallel while loop, which is time controlled with a loop timer into a flat sequence. The acquiring and writing in the AO module are synchronized by an occurrence scheme.

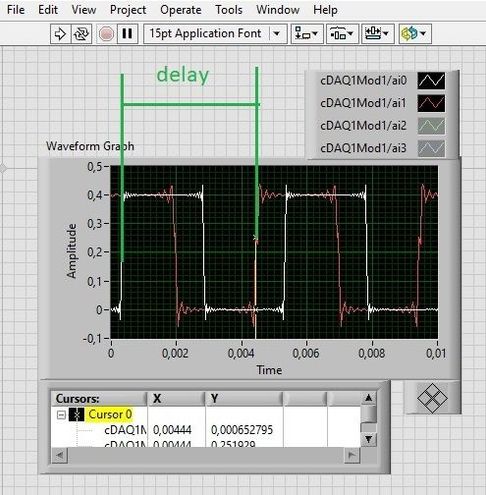

An external chassis, which is capable to generate an arbitrary frequency square signal and read it with the target AO signal is used to observe the delay between the "excitation signal" (white color in fig. below) and the signal produced by the NI 9264 (red color in fig. below). From the figure below, where a 200 Hz square signal was used, a delay of approximately 4ms is observed. If the loop period is to be 0.1ms, we are observing almost 40 times the period!

I do not know what am I doing wrong, and if there are any stored acquired data in the buffer when I use the NI 9239 in the FPGA interface, producing such delay. I have just tried to connect the FPGA I/O node for the AI modules directly to the Output nodes, nevertheless I get the same results. When I increase the sample rate (e.g. 25 kHz), the delay reduces to 1.6 ms approximately. We have some timing functions to monitor the loop elapsed time, and it seems not to be a problem with the loop period.

In summary, I intend to use a FPGA device to read some analog inputs and return with those same signals by means of an analog output module. The signal is produced, however such signal is delayed more than 5 times the loop time.

Does anyone had the same problem? Is there any example combining the FPGA with AO and AI modules? When I searched for examples for the previous mentioned modules, I found only vi's which acquire the data and send it to the host to be displayed in a Waveform graph.

Thank you

11-20-2020 06:39 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have just found the following link, and it seems to have an explanation for my problem.

Does it make sense?