- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Empty Array Given by SubVI (potential race condition)

Solved!12-16-2020 11:30 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I am an amateur programmer in LabView and have been attempting to adjust the design philosophies I've learned in Object Oriented programming to fit the data flow model and philosophies of LabView.

That being said, this problem could boil down simply to a misunderstanding of that philosophy and/or a mistakenly implemented form of that concept. Here is the problem at its core: When I run a subVI in my main.vi program it outputs an Empty Array. However when I step in and view each step individually, including into the subVI, the problem doesn't exist (hence my suspicion that I've unintentionally set up a race condition).

In my main VI I have a sub vi that has data flowing in, the snippet is that VI up close. I can't share the entire main vi for job related development reasons but hopefully my sharing of the subVIs will be enough.

You'll be able to see the data types and objects I'm passing through and passing out of each VI. The sub-sub-VI 7.2_cycle1_Test.vi is intended to send a voltage out to a regulator, read in pressure from an inlet pressure gauge, compare that pressure to a constant set of parameters and end the loop upon success. Failure is monitored by whether or not this loop completes within 6 seconds using the Time Elapsed module. If 6 seconds have passed and the pressure in has still not met the requirements, the loop is ended, the boolean value in the array corresponding to this particular index is set to False, and everything moves on.

Note: I have not actually implemented the Write task that would send out the voltage to the regulator as I'm not currently hooked up to the DAQ that I will eventually interface with. My read in function is depending on a virtual channel that produces a voltage between 0 and 5 volts (corresponding to pressure transducer signals) which in turn will produce a wave that oscillates between 0 and 5. Coincidentally it takes roughly 1 second in my runs for this wave to reach a value that falls within the constant parameters in 7.2_cycle1_Test.vi.

Despite the sub-subVI succeeding in 1 second, I receive an empty boolean array on its parent VI 7.2_Cycle_Profile_Cycle1_Test.vi and of course its parent VI my main.vi.

It seems like the subvis are being run asynchronously which doesn't make sense to me as the rest of both parents are dependent on the data from the child VIs.

I know sharing my main.vi would help out more than my typing a ton, but that's not an option. However I have attached both subVIs and I hope that will help anyone who is willing to help me out and lend some criticism.

Thank you

Solved! Go to Solution.

12-16-2020 11:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

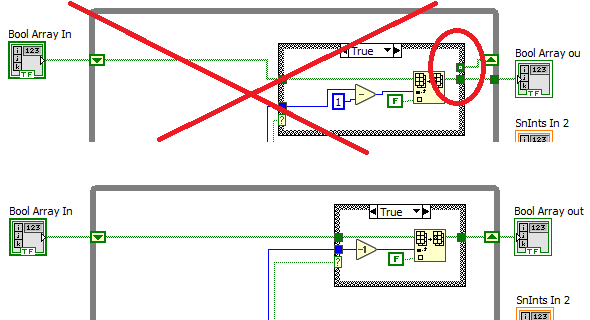

In your subVI, you a setting the boolean array in the shift register to an empty array as soon as the timer has not elapsed, i.e. instantly.

Eliminate the "use default if unwired" output tunnel and use the other tunnel to go back to the shift register. Wire the output terminal to the outside of the shift register.

12-16-2020 11:50 AM - edited 12-16-2020 12:10 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Depending on what else is going on, you could also just eliminate the shift register, of course. You don't really need it here.)

My earlier explanation graphically explained:

12-16-2020 11:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Altenbach, I think this is going to work my shining Knight of NI.

I'm going to make these changes to my subVIs and test it out. But in the meantime something that confuses my is this "use default if not wired" option. In my mind that means if a particular tunnel of a case structure is not wired for the given case, that whichever is the default case, that tunnel's value is used. In my example the default is False (I believe?) and in my false case I simply pass through the boolean array unchanged. Would this not be what the true tunnel sends out? Why is it empty at that stage?

Thanks so much for the reply and I'm looking forward to getting these changes made and seeing this data as it should be.

12-16-2020 12:10 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

A few more comments on style:

- You don't really need output terminals that just return the input unchanged. (sysInt 2, Valve out)

- Unless the subVI opens the front panel and the user is supposed to change controls while the loop is running, All input terminals belong before the loop.

- Error out should be after the loop. Maybe you also want to terminate on error.

12-16-2020 12:16 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

That is all great advice, thanks again Altenbach,

Me putting the unchanged variables into the subVI was me desperately trying to find the solution thinking that all data into the parentSubVI had to flow into the child too or else it would be asynchronous. Obviously that is not the case I just had a misunderstanding of the very basic premise of the Use Default if Unwired class haha. I now know that refers to default data, not default case.

The solution worked and you've been a great help!

Cheers