- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Build array into timed cycle loop FPGA

09-29-2014 04:05 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

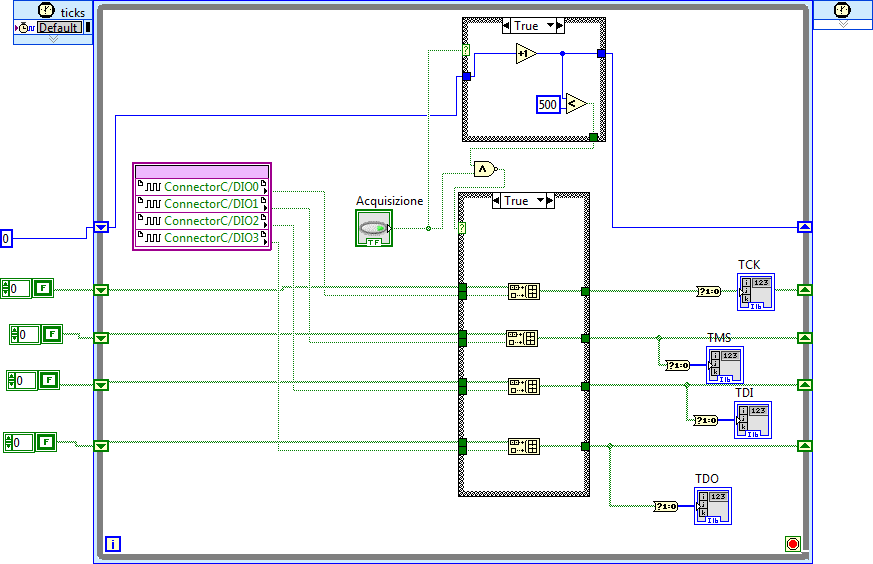

Hi, I'd like to acquire four digital signals with MyRIO fpga when i click an "acquire" button and put them in four arrays of 500 elements each. I made this:

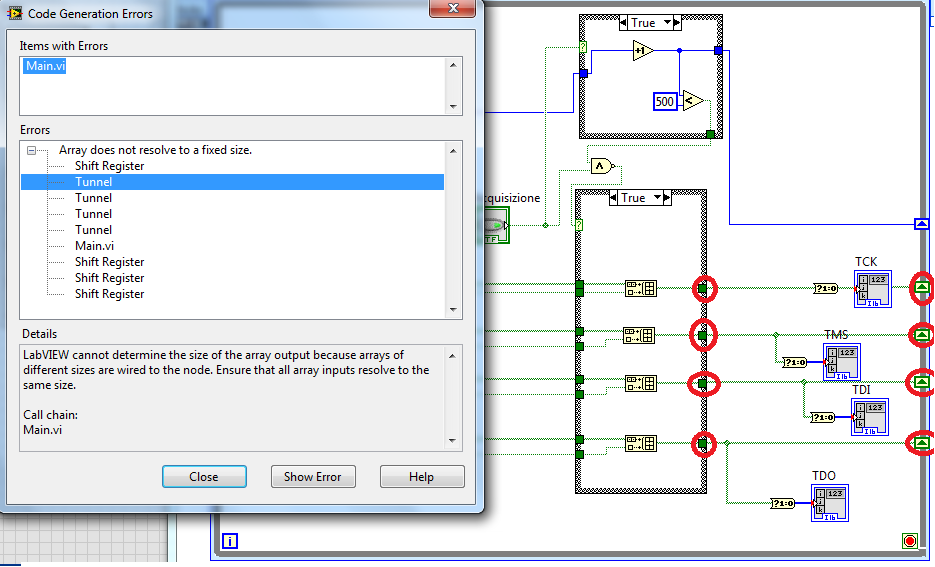

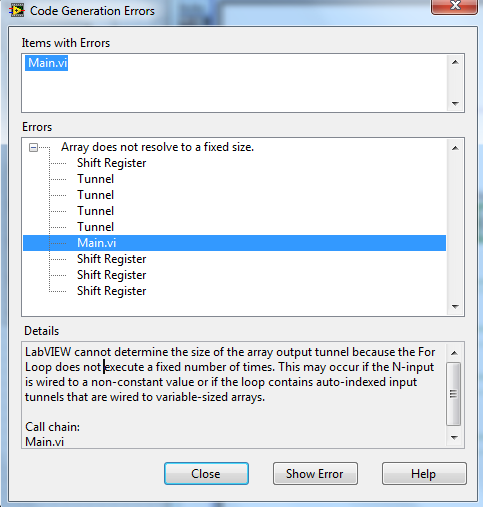

but I receive these errors:

I have defined fixed arrays at the start of the cycle. What is the problem?

09-29-2014 04:15 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

use an indexer/counter to put the data into your array .... append will not work

09-29-2014 04:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

09-29-2014 04:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

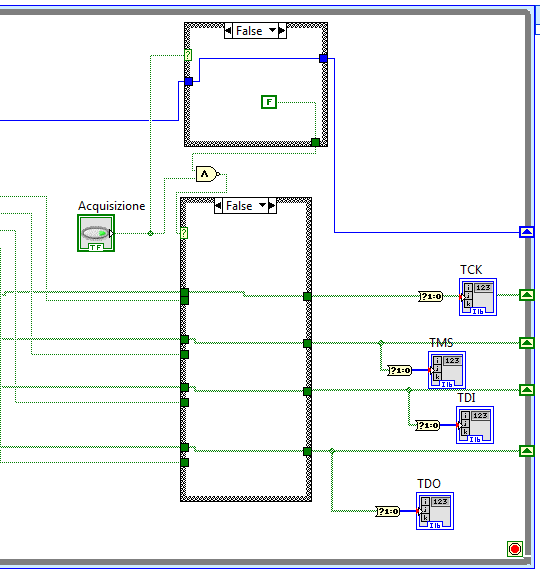

Thanks guys. Is this a good way to acquire a digital signal? Are there better ways/express VI to do this basic task?

09-29-2014 05:03 AM - edited 09-29-2014 05:03 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

When using replace instead of build array this way is ok, but it really depends on what you do with the data afterwards. Do you need to convert each bit to a I16 (throwing away 15 bits of the I16)? That will consume a lot of resources, 4 arrays of 500 I16 elements each. What do you do with the I16 arrays afterwards?

09-29-2014 05:07 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

First, I want to show these bit as zeros and ones, not with LED. I know this is a bad way to do because I waste 15 bit!

09-29-2014 05:10 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Show where? On the front panel of the FPGA VI?

09-29-2014 05:11 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

yes

09-29-2014 05:14 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Well then this looks like a test application anyway, in that case I would not worry about inefficiency as long as the code fits on the FPGA.

09-29-2014 07:03 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

An FPGA does not have a front panel. When you compile an FPGA, you are difining actual gates on the FPGA. There is no display once it is deployed. What you want to do is put these values into a DMA FIFO to pass the data up to the Real Time program. You can technically show that front panel. So your FPGA should just read these digital lines and put them in the FIFO. No need for arrays in the FPGA. The RT code can then build arrays, if you really want to do that. But it is still better if you predefine your array and then replace elements as you go (a lot more efficient for the memory).

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5