- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »

Accessing Same ADC channels in Different loops

Solved!05-29-2018 06:38 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Moonnight786,

Checking your VIs, I see that you are using the DataSGL DMA FIFO to send the acquired values from the FPGA to the RT. I think my first troubleshooting step would be there, to check if the problem relies on the FPGA not sending the required amount of data points, or the RT not handling them correctly. You can perhaps ask for more than 1023 elements in the buffer.

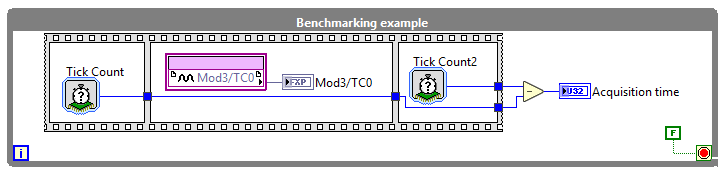

Moreover, I would benchmark your FPGA acquisition VI to see if it is acquiring at that speed. I remember we talked in another forum post about using this 9207 as a non-Delta-Sigma module as we don't have Data Rate input:

All the best!

05-30-2018 01:00 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello OSCAR:

I did benchmark my FPGA loop, it is exactly working on 500s/s. should I try to change my buffer size, yes NI 9207 is working in Non- delta sigma settings, and I took data the output is fine, I just seeing trouble while data logging.

Thank you

05-30-2018 05:02 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Moonnight786,

I noticed something interesting in your RT VI. Seems to me that you are destroying the Queue that you use to transfer the elements from the producer to the condumer loop, before the latter one has had time to process all of them.

I recommend you make sure that the queue has time to dequeue all the elements that you acquire, before releasing the reference:

Let us know your results. All the best,

05-31-2018 03:26 AM - edited 05-31-2018 03:27 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

OSCAR

Bundle of thanks for your input to my problem, I did edit my code as you advised and also I debug my FPGA side again and I found the problem, when I use NI 9381 module alone it works as expected and also producing data logging at 500S/s is correct, same thing I tried with NI9207 module but it max speed goes up to 137Hz, this is the main cause of slowing down my data logging for the whole project.

I have two question now.

Q1: Can I use two parallel while loops to read two different modules on FPGA side and then I read both in RT.vi separately, or in the same loop.

See attached file. for Q2

Q2: What is 500S/s aggregated means?

Does it means that (500S/s )/ number channels

as in high-speed mode, I am getting the 137Hz frequency that kind of proves it as I am only using 4 channels on this module.

Moonnight.

05-31-2018 06:14 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Moonnight,

Glad I was able to help. To answer your questions:

Q1: Can I use two parallel while loops to read two different modules on FPGA side and then I read both in RT.vi separately, or in the same loop.

Yes, you can use multiple parallel loops in your FPGA. Remember that an FPGA, unlike a processor, does execute all operations parallel when they are set that way, since they use different hardware resources in the FPGA fabric.

Q2: What is 500S/s aggregated means?

That 500 S/s aggregated rate means that the ADC can convert 500 samples every second, and it will be shared between the channels you use. For 4 channels, I would expect a maximum rate of 125 S/s. When a card supports simultaneous sampling, you will see it written as "S/s/ch".

All the best,

06-01-2018 11:19 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Oscar

Thank you so much

- « Previous

-

- 1

- 2

- Next »