- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA Resampling -- Output timestamp is saturated

08-31-2017 07:20 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I've been debugging an power analyzing station and I discovered the FPGA Resampling vi is returning a resampled element with a (practically speaking) saturated timestamp. I'm giving it the number of seconds since Jan 1, 1970 as a FXP <+, 64, 32> number (roughly 1,504,198,487) and the Resampled Element cluster always contains a return timestamp of roughly 4,294,967,295.9991xxx.

I feel like I'm missing something simple, but I have no idea what it might be. Has anyone ever encountered this?

09-01-2017 03:45 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I can't explain the problem but I can explain what I'm doing but it sounds similar.

I take the ns counter from the FPGA timekeeper - convert to seconds to the same representation (unsigned 64,32 FXP) including the UTC correction.

This hasn't given me any timestamp issues under 2015.

========

Ask me about Rust & NI Hardware

My writings are at https://www.wiresmithtech.com/devs/

09-01-2017 12:07 PM - edited 09-01-2017 12:24 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi James,

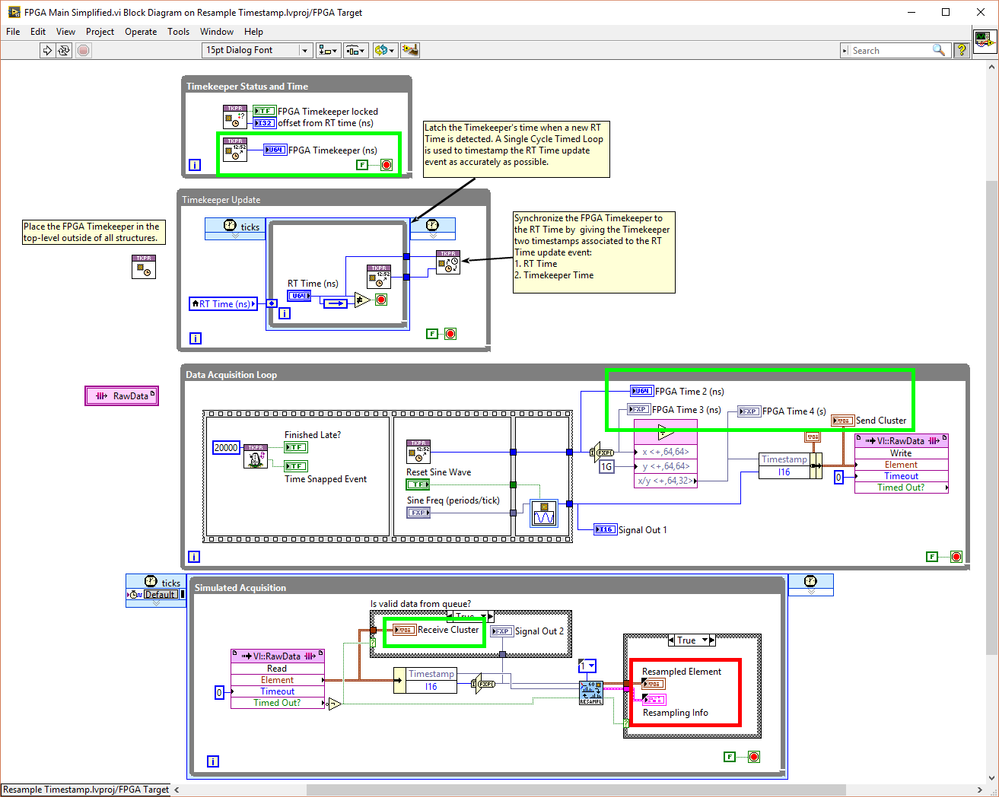

I've included a small project (including bitfile) that reproduces what I'm seeing. Here's the FPGA block diagram:

The green rectangles highlight locations where I can monitor the timestamp sent by the Timekeeper. The red rectangle is where I get the saturated timestamp.

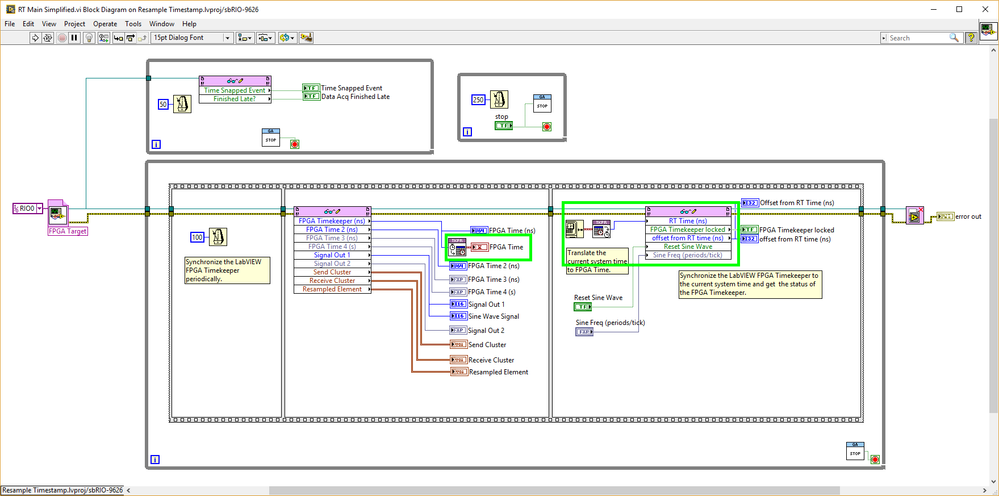

My RT block diagram is extremely simple:

The green rectangles show where I read the Timekeeper and convert it to a readable date and update the Timekeeper with RT time.

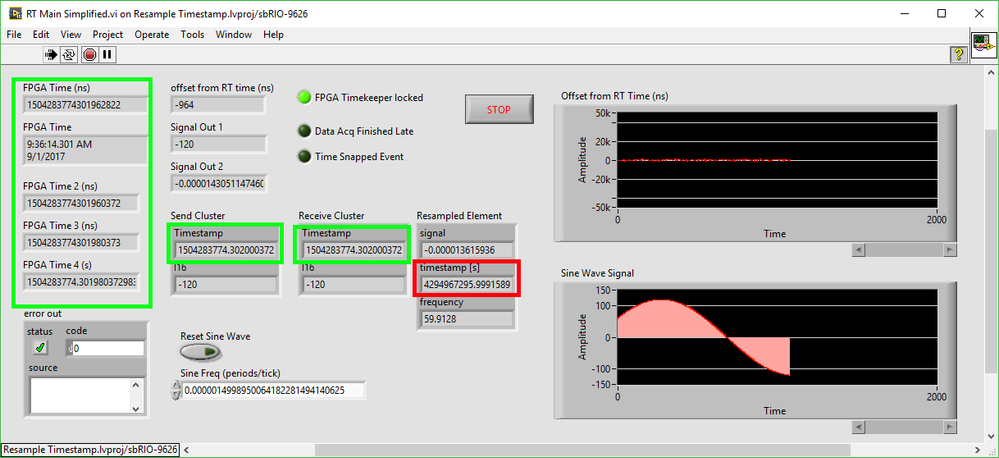

This is what the RT front panel look like when I run it:

The rectangles here correlate to the green and red rectangles on the two block diagrams. As you can see, the timestamp returned by the Resample vi is very nearly saturated.

Can you please try the code on your system and see if you get the same behavior? This is with LabVIEW 2015 sp1 and an sbRIO-9626 running LV Real-Time 15.0.1 from Feb 2016 (v15.5). For testing, I'm downloading the FPGA code to the FPGA then running the RT code interactively.

09-04-2017 04:29 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Daklu,

All my systems are tied up in a long term test right now but that will finish in a couple of days and I can give it a go then.

Cheers,

James

========

Ask me about Rust & NI Hardware

My writings are at https://www.wiresmithtech.com/devs/

09-15-2017 06:39 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

James,

Have you had a chance to try out this code and see if you get saturated timestamps as well?

09-18-2017 12:21 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Daklu,

Managed to give it a go today. On a cRIO-9024 (9113 chassis) it is showing no problem. This is under 2015 SP1f7.

Only thing I've done is added a new target to the project and dragged over the VIs.

Not entirely sure what that means!

========

Ask me about Rust & NI Hardware

My writings are at https://www.wiresmithtech.com/devs/