ni.com is currently undergoing scheduled maintenance.

Some services may be unavailable at this time. Please contact us for help or try again later.

NI USRP RIO Full Ethernet Support Reference Architecture

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Products and Environment

This section reflects the products and operating system used to create the example.To download NI software, including the products shown below, visit ni.com/downloads.

- RF|Wireless

Hardware

- FPGA Xilinx Compilation Tools

- LabVIEW 2015 SP1

- LabVIEW 2020 SP1

- LabVIEW FPGA Module

Software

- NI-USRP

Driver

- Windows

Operating System

- LabVIEW G

Programming Language

Code and Documents

Attachment

Description

Description-Separate-1This document explains how to install, configure, and test the National Instruments universal software radio peripheral (USRP) 294xR or 295xR device with the new Ethernet-based Reference Architecture. This Reference Architecture configures the USRP RIO and passes TX/RX data all through the Ethernet Port while having a customized FPGA code pre-deployed.

This updated version splits the project into a Host Project and an FPGA Project. This has been done to allow for the modification and compilation of the FPGA but the compatible environment for the FPGA project is limited to LabVIEW 2015 SP1 due to the limited compatibility of the FPGA CLIP and the Xilinx IPs with the Vivado compilation tools.

The Host project does support the latest LabVIEW versions starting with LabVIEW 2021 SP1.

(*) TwinRX USRPs are not yet supported by this architecture.

Description-Separate-2

How to Use

How-Separate-1To use the NI-USRP instrument driver, your system must meet certain requirements. Refer to the product readme, which is available on the driver software media or online at ni.com/manuals, for more information about minimum system requirements, recommended system, and supported application development environments (ADEs).

Required Hardware

- NI 294xR or NI 295xR – NI-2945& NI 2955 TwinRX USRPs are not supported

- AC/DC Power Supply and Power Cable

- 10 Gbit SFP+ Ethernet Cable

- Computer with available 10 Gbit Ethernet interface*

- NI PCIe-MXI Express interface kit for USRP RIO**

Installing the Software-Host Project

You must be an administrator to install NI software on your computer.

- Install LabVIEW 2021 or later and the corresponding LabVIEW FPGA version.

- Download the NI USRP driver software corresponding to your LabVIEW Version or above.

- Install the driver by following the instructions in the installation wizard.

- When the installer completes, restart your computer.

- Extract the folders from the zipped file named Drivers Support which you got with the Reference Architecture material

- Back up the folder instr.lib in the LabVIEW install folder in case you need to revert back to the stock USRP Driver files.

- Copy-Paste the extracted instr.lib folder in the LabVIEW install folder: C:\Program Files (x86)\National Instruments\LabVIEW 202x

- When prompted, choose to replace all, this will replace the older version of the Library.

- Copy-Paste the USRP RIO Full Ethernet Support Host folder, provided to you with the Reference Architecture material, to the root directory of your hard drive (C:\).

- Open LabVIEW and the project and resolve any conflicts detected by LabVIEW***

|

(*) You can find the recommended 10Gbit Ethernet card in this link for the PCIe version. For the PXIe version, you can find the recommended card at this link. (**) This PCIe-MXI interface kit will only be used to deploy the bitfile to the Flash of the USRP RIO the first time (***) Considering that we are changing folders and deploying the project, you need to specify the new locations for the project dependencies |

Installing the Software – FPGA Project

You need to install the required software for the FPGA project on a separate computer or virtual machine. This setup will only be used to modify and compile the FPGA. You must be an administrator to install NI Software on your computer.

- Install LabVIEW 2015 SP1 with the corresponding version of the FPGA module.

- Download the NI USRP driver software version 15.5.

- Install the driver by following the instructions in the installation wizard.

- Download and install the LabVIEW FPGA Compilation Tool for Vivado 2014.4 version 2015 SP1.

- When the installer completes, restart your computer.

- Extract the folders from the zipped file named Drivers Support which you got with the Reference Architecture material in the FPGA project folder.

- Backup the folder instr.lib in the LabVIEW install folder in case you need to revert to the stock USRP Driver files.

- Copy-Paste the extracted instr.lib folder in the LabVIEW install folder: C:\Program Files (x86)\National Instruments\LabVIEW 2015 SP1

- When prompted, choose to replace all, this will replace the older version of the library.

- Copy-Paste the USRP RIO Full Ethernet Support FPGA folder, provided to you with the Reference Architecture material, to the root directory of your hard drive (C:\).

- Open LabVIEW and the project and resolve any conflicts detected by LabVIEW.

Compiling the FPGA

You can either use the already compiled bitfile that matches the last version of the main FPGA VI or recompile the FPGA if you want to bring additional functionality to the FPGA personality.

- Verify that the CLIP is correctly added and that the MGT Socket has the correct CLIP declaration.

- Verify that the FPGA VI doesn’t show a broken arrow.

- Create or update the build specification for the main FPGA VI.

- Right click on the build specification and select build.

- You can choose to either compile the FPGA locally (*) or use a cloud compilation solution.

- When the compilation is done, copy the generated bitfile to the computer with the Host Project in the FPGA Bitfiles folder

|

(*) Compiling the FPGA locally is subject to limitations if your operating system is Windows 10. Make sure to check this link for the compatibility of the compilation tools with Windows 10. |

Installing the Hardware

Install all the software that you plan to use before you install the hardware.

Setup needed to deploy the FPGA bitfile:

- Power off the computer and the USRP device.

- Plug-in the MXI Express Interface Kit to connect the USRP device to the computer.

- Connect the MXI device to the USRP device using the included cable.

- Power on the USRP device then power on your computer.

Setup needed to run the Reference Architecture:

- Power off the computer

- Plug in the 10Gbit Ethernet Card into an appropriate PCIe slot in your computer

- Connect the SFP 0 port of the USRP RIO* to the 10Gbit Ethernet card using the SFP+ cable

- Power on the computer and the USRP RIO

Setting Up the Network

You must configure your 10Gbit Ethernet Card to accept large packets:

- Right-click My Computer and select Manage

- Select Device Manager

- Under your Network Adapters, double click the port that you’ll be using

- Go to the Advanced tab and select the Jumbo Packet

- In Value select the 9014 Bytes

- Press OK and close the Device Manager

|

(*) The USRP RIO that you will be using should already have on its flash the bitfile shipped with the Reference Architecture |

The default IP address for the SFP 0 Port of the NI 294x or NI 295x is 192.168.30.2.

- Ensure the host computer uses a static IP address. You may need to modify the network settings for the local area connection using the Control Panel on the host computer. Specify the static IP address in the Properties page for Internet Protocol Version 4 (TCP/IPv4).

- Configure the host Ethernet interface with a static IP address on the same subnet as the connected device to enable communication, as shown in the following table.

|

Component |

Address |

|

Host Ethernet interface static IP address |

192.168.30.1 |

|

Host Ethernet interface subnet mask |

255.255.255.0 |

|

Default SFP 0 port device IP address of the USRP |

192.168.30.2 |

You can change the IP address of the SFP 0 port of the USRP by the following steps:

NOTE: Make sure that the default personality is the one deployed on the FPGA

- Connect the SFP 1 Port to the 10Gbit Ethernet card using the SFP+ cable

- Set the IP of your 10Gbit Ethernet card port to 192.168.40.1*

- Verify that your device is on

- Select Start>>All Programs>>National Instruments>>NI-USRP Configuration Utility

- Select the Devices tab of the utility. Your device should appear in the list on the left side of the tab.

- In the list, select the device. The IP address of the selected device is displayed in the Selected IP Address

- Enter the new IP address in the New IP Address textbox

- Select from the Select Port drop-down menu the Port 0 (10G) to indicate that the new IP will be for the SFP 0 port with a 10Gbit interface

- Click the Change IP Address button to change the IP address

- The utility prompt you to confirm your selection. Click OK to proceed

- The utility displays a confirmation to indicate the process is complete. Click OK

- Power cycle the device to apply the changes

|

(*) The default IP Address of the SFP 1 port of the NI USRP RIO is 192.168.40.2 |

Deploying a Customized Bitfile on the Flash

This reference architecture comes with an open source LabVIEW FPGA code which allows you to add your customization to the FPGA code while keeping the 10Gbit Ethernet support. You can either directly flash the provided bitfile ‘Ethernet Full Support Xcvr.lvbitx’ in the FPGA bitfiles application folder which supports 10Gbit Ethernet or build from the source FPGA. After compiling your FPGA code, you can deploy its bitfile to the Flash of your device by the following steps:

- Refer to the Installing the Hardware section and make sure you follow the instructions of the setup needed to deploy the FPGA bitfile

- Launch the NI Measurement and Automation Explorer

- Under My System, expand the Devices and Interfaces and select the RIO target representing your USRP RIO

- On the Settings tab, Select Autoload on reboot option from the Firmware Autoload Setting drop-down menu

- Click the Update Firmware button

- Find and select the bitfile that you’d like to load on the Flash. Click Open

- Click the Begin Update button and wait for the upload to finish

- Turn off your computer

- Turn off your USRP RIO

- Disconnect the MXI cable

- Turn on your USRP RIO

- Turn on your Computer

The new bitfile is loaded now on the FPGA of your device.

Running the Reference Architecture

You can run the Reference Architecture by following the below steps:

- Make sure you have deployed the bitfile shipped with the reference architecture

- Make sure that the IP of the 10Gbit Ethernet card and the IP of the SFP 0 of your device are on the same subnet. If the SFP 0 still has its default IP: 192.168.30.2, you can have your computer IP set to 192.168.30.1

- Open the USRP RIO Full Ethernet Support Host>>USRP RIO Full Ethernet Support Host.lvproj and run one of the host VIs.

- The first time opening of the project will require you to fix certain dependencies due to the replacement of some of the USRP drivers.

- Click on the Resolve Conflicts button in the LabVIEW Project

- Choose the right file for each conflict.

- Once it is done for all the VIs, save the project by clicking on File then Save All.

- Before running any of the host VIs make sure that you have selected the correct daughterboards for your USRP. A mapping between the NI USRP hardware and Ettus Daughterboards used is available here.

How-Separate-2

Example code from the Example Code Exchange in the NI Community is licensed with the MIT license.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Hi,

Very interesting project; i don't know if i have done something wrong or not, but i followed all the procedures and i can't execute the template due to an error on " niUsrpRio Config v1.lvlib: Chekc Data Clock Rate and Bandwidth - Ethernet.vi": Type Definition 'Daughterboard ID': Type definition not found or contains errors - The master copy for this type definition could not be found or the master copy has errors. You must find and fix the master copy, or right-click this type definition and select Disconnect. Could you tell me how to solve this error?

Moreover, if i change the FPGA script, could i load it on board with UHD using ethernet connection?

Thanks for the help!

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

I've followed the procedure and i've loaded the bitstream into the device, but when i ping the device, i receive no answers; it seems that the device is not connected, also because the device is not listed on configuration utility tool. Can i have some advices in order to use this code?

My scenario is a NI USRP 2954R connected with MXI cable to a PC with NI PCIe 8371, and the ethernet connection based on ethernet cable connected to the USRP with a SFP+ to Eth adapter on port 0, and a usb network adapter on PC side.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Hi,

I'm also unable to execute the host VIs as I've also encountered the same error as mentioned above. Following are the errors that I get:

1) "NI USRP driver support for LabVIEW 2019 is missing and is referenced by the following VIs:

-C:\Program Files\National Instruments\LabVIEW 2019\instr.lib\niUsrpRio\Config\v1\Host\Private\Check Data Clock Rate and Bandwidth - Ethernet.vi

When I open the above VI, I get the following list of errors:

2) This VI is connected with a library that does not include the VI. The VI might have been deleted from the library. Add the VI to the library again or select File»Disconnect from Library.

3)The master copy for this type definition could not be found or the master copy has errors. You must find and fix the master copy, or right-click this type definition and select Disconnect.

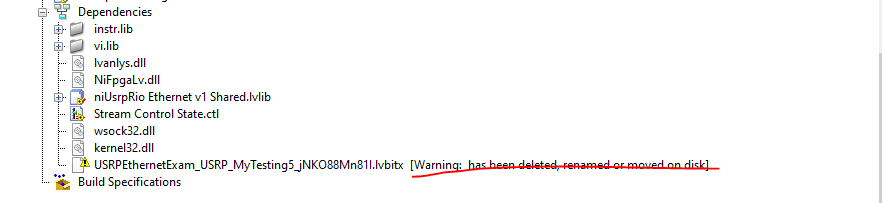

4) When I opened the host VI, I also noticed that the VI was unable to find a .ctl file and loaded the VI without it. I manually browsed to that directory and couldn't find the .ctl file it was looking for. This is shown in the snapshot below.

Kindly advice me how to get around this issue. Any advice or help will be really appreciated.

Thanks in advance.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

I have resolved the aforementioned issues by adding all the ethernet-based VIs in the library (niUsrpRio Config v1 Host.llb). You can select skip in the dialogue that appears for password protected VIs when adding them to the library.

Ethernet VIs can be found in the Public and Private folder found in this path:

C:\Program Files\National Instruments\LabVIEW 2019\instr.lib\niUsrpRio\Config\v1\Host

Also, usrpDboardld.ctl file is located at the path given below. Make sure to manually browse and load this file when you open any host template VI.

C:\Program Files\National Instruments\LabVIEW 2019\instr.lib\niUsrpRio\Config\v1\Host\Private\usrpDboardld.ctl

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Hi,

I am using USRP X310 with Twin RX Daughterboard.

What kind of changes i should made in the given example code "USRP RIO Full Ethernet Support.zip 18429 KB" to run this code on my target.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Hi,

This example code just do not compile without any changes. It returns error during intermediate files creation, saying labview cannot determine data size in several places. I double and triple-checked it, tried LabVIEW versions from 2019 to 2021. It seems that the dependency on niInstr Ethernet MAC - CLIP v1.lvclass or niInstr AXI4-Stream Reader/Writer v1 FPGA.lvclass changed since this architecture was created. I tried modifying the involved VIs assuming the sizes of tdata or tkeep to be largest possible (high-throughput streaming), and was able to compile the bitfile, but the communication with the target does not work with my changes.

BTW the bitfile provided with this architecture works well providing IQ data over ethernet. Which means, the FPGA VI is OK to compile on some circumstances (e.g. compatible dependency versions).

Is there anyone succeeded with compiliung the working bitfile?

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

A new version of the architecture has been uploaded and should allow you to work around the issues encountered with the compilation of the FPGA VI. The core IP used in this project is only compatible with LabVIEW 2015 and the corresponding Vivado compiler, it is the reason why in this new version of the architecture, the host and FPGA project has been split. The FPGA project will remain on LabVIEW 2015 to allow recompilation while the host project can be used in the latest LabVIEW versions starting LabVIEW 21.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Hi keloueldrhiri, is there a way to adapt the above reference on 1Gbit connection?

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Hello,

I am Using NI 2954R USRP with 1Gbit ethernet interface. Does this reference architecture support 1Gbit ethernet interface? If not, could you please help us with possible ways to support on this.

Are we able to run this Reference architecture of FPGA in LabVIEW 2018?

Thanks.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

I have successfully compiled this bitfile following all the instructions. I downloaded LabView 2015 SP1 and its FPGA module, Xilinx Compilation Tool 14.4 , USRP 15.5 for the compilation of the FPGA bitfile. Then, I download the bitfile to the flash of USRP 2954R.

I also copied the compile bitfile Ethernet Full Support Xcvr.lvbitx to the FPGA biftiles holder of the Host project. I open the host top-level project Rx over Ethernet.vi, resolved all of the conflicts but the following one:

USRPEthernetExam_USRP_My testing.....

So the host VI is still broken.

My initial aim is to use the 1Gbit port which the project doesn't support. I just want to see if it is possible to modify the project in a way that is suitable for streaming using 1Gbit port. Is it possible for the original developer to offer some suggestions. I think it is possible technically feasible if the actual data sampling rate is low. For 1Gbit port , the IP of the host if 192.168.10.1, and it is 192.168.10.2 for the USRP target.