LabVIEW FPGA I2S Decoder

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Products and Environment

This section reflects the products and operating system used to create the example.To download NI software, including the products shown below, visit ni.com/downloads.

- CompactRIO|SingleBoardRIO

- PXI|VXI

Hardware

- LabVIEW FPGA Module

- LabVIEW

Software

- NI RIO

Driver

Code and Documents

Attachment

This example demonstrates how to decode digital I²S bus data into audio channels with LabVIEW FPGA.

Description

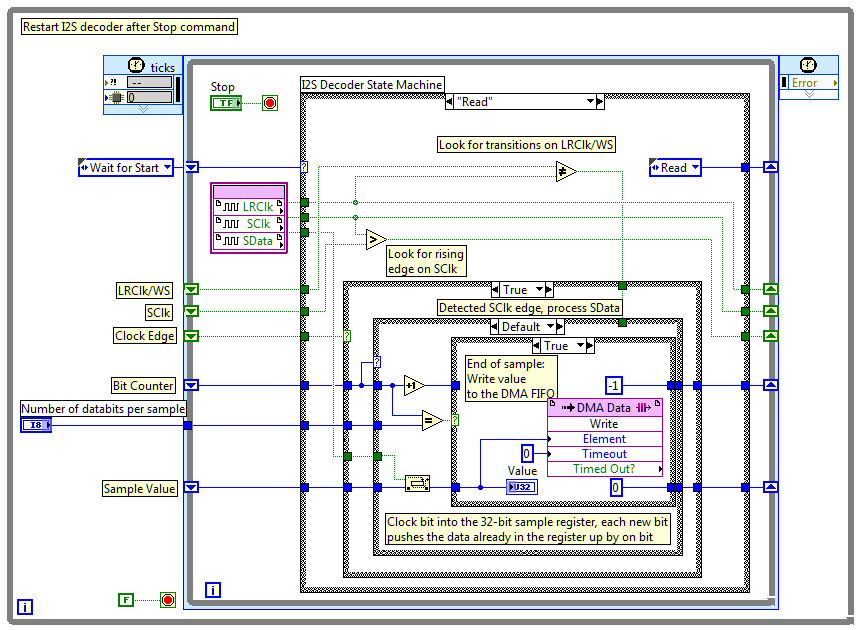

The example demonstrated how to decode a I²S signal using LabVIEW FPGA. The code can be used on most LabVIEW FPGA targets (e.g. R series, CompactRIO) that support high-speed digital input. I²S is used to encode digital audio data within systems and components. For example digital audio inside of an MP3 player or DVD player is commonly communicated using the I²S protocol.

The example uses a Single Cycle Timed Loop in the FPGA diagram to monitor the three signals of the I²S protocol.

It monitors the LRClk (WS) and SClk lines looking for signal transitions/edges, and collects data bits from the SData (SD) line, writing completed audio samples to a DMA buffer for transfer to the host VI.

Requirements

Software

- LabVIEW Full Development System 2012 (or compatible)

- LabVIEW FPGA Module 2012 (or compatible)

- LabVIEW Real-Time Module 2012 (or compatible), if you use a RealTime Target for the Host VI

Hardware

- You have to migrate this example to your LabVIEW FPGA Target. You must recompile the FPGA VI.

Steps to Implement or Execute Code

- Download and open the attached ZIP-file

- Open the [Host] Display I2S Data.vi inside the LabVIEW project and follow the instructions on the Front Panel

Additional Information or References

**The code for this example has been edited to meet the new Community Example Style Guidelines. The edited copy is marked with the text ‘NIVerified’. Read here for more information about the new Example Guidelines and Community Platform.**

Discussion Forum Thread on I2S: http://forums.ni.com/t5/Components/I2S-Encoding-and-Decoding-Signals-in-LabVIEW/td-p/959062

Example code from the Example Code Exchange in the NI Community is licensed with the MIT license.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

The I2S Specification link above actually links to an I2C Specification.