LV FPGA Pseudo Random Number Generator

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

Products and Environment

This section reflects the products and operating system used to create the example.To download NI software, including the products shown below, visit ni.com/downloads.

- LabVIEW FPGA Module

- LabVIEW

Software

Code and Documents

Attachment

Overview

LabVIEW FPGA VI and example showing how to generate pseudo random numbers using a linear feedback shift register algorithm.

Description

The Pseudo Random Number Generator VI is built as an IP core for LV FPGA and can be used in a variety of applications. The VI is set to be reentrant so that it can be used multiple times in an application.The linear feedback shift register algorithm used to generate the pseudo random number is explained in detail in this Wikipedia article.

Requirements

- LabVIEW 2012 Full or Professional Development System

- LabVIEW 2012 FPGA Module

Steps to Implement or Execute Code

To simulate this algorithm on a development computer:

- Open "Pseudo Random Generator 2012 NIVerified.vi " and run it to show random values populating on the chart.

- Open the "Pseudo Random Number Generator (FPGA) 2012" to examine how this is accomplished.

To implement this on an FPGA target:

- Add the "Pseudo Random Number Generator (FPGA) 2012" and "Pseudo Random Generator 2012 NIVerified" VIs to your directory and/or project.

- Use the "Pseudo Random Generator 2012 NIVerified" as your FPGA VI, then compile and run this example interactively to notice the numbers populating

Additional Information or References

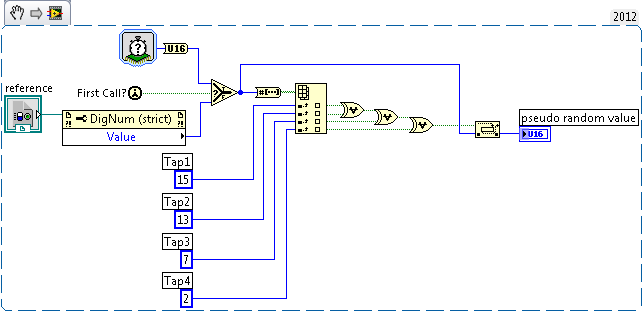

VI Snippet of Pseudo Random Generator 2012 NIVerified.vi

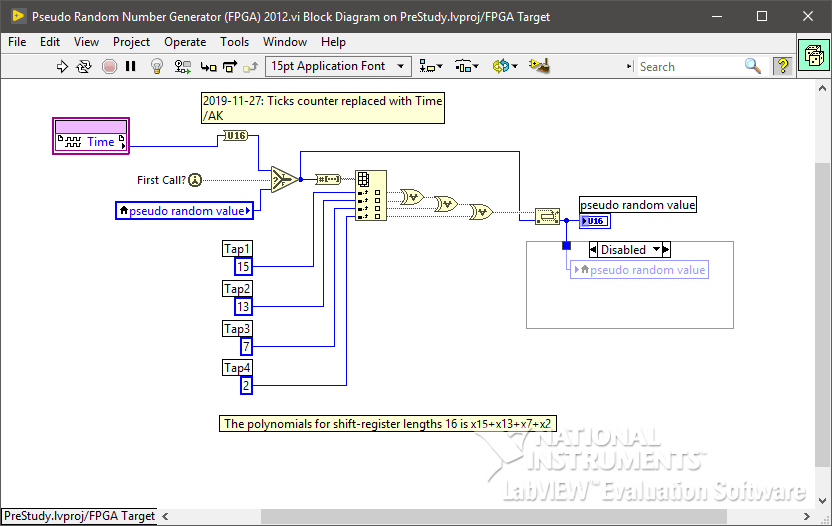

VI Snippet of Pseudo Random Number Generator (FPGA) 2012

**This document has been updated to meet the current required format for the NI Code Exchange. For more details visit this discussion thread**

Example code from the Example Code Exchange in the NI Community is licensed with the MIT license.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

Thanks for idea!

Unfortunately, this generator does not work in LabView 2019 in cRIO/FPGA simulation mode. It returns always 0. Probably this is due time/tick counter giving first value equal to 0.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report to a Moderator

A little modification to make it run on cRIO-9048 "simulated RT/FPGA mode" in LabView 2019. (for unknown reason I cannot add VI as an attachment).