- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SMU as Ammeter to Measure Current

11-30-2012 04:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I would like to do something similar to what is discussed in the following thread using multiple channels of a PXI-4141 4-channel SMU:

http://forums.ni.com/t5/Digital-Multimeters-DMMs-and/SMU-used-for-current-measurement/td-p/1297856

I would like to understand the statement in the final post of that thread regarding burden voltage/shunt resistance. In my application, it is critical that I compensate for the presence of a shunt resistor when I take a current measurement. How do I determine what the effective shunt resistance or the effective burden voltage might be when using the current-measurement capabilities of the SMU?

Thanks!

Jeff

11-30-2012 06:27 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Jeff,

Any burden voltage generated across the internal shunt resistor of the SMU will be cancelled out by the internal supply of the SMU, leaving your overall voltage drop essentially 0V. If you program your SMU voltage to 0V, the SMU will try to maintain this value across its terminals. The only voltage drop you may want to consider is the offset accuracy of the SMU which is spec'd at +/-150 uV. This is not a function of the voltage drop across the SMU shunt but rather just the measurement/output accuracy of the device itself.

As far as whether to disable the output vs programming 0 V, when the 4141 is in the disabled state, the SMU will be set to 0V (just like the 4130), but will be set to 2% of current range instead of 20 mA. See this KB for more information on that. Therefore, on the 4141, when deciding to use the 'output disabled' vs 'output enabled' at 0V, the 'output enabled' case will allow customizable control of the current level whereas 'output disabled' will always be 2% of range. In either case, I suggest that you pick the lowest current range possible for your measurement so that you have the best resolution and accuracy possible.

Can you explain how your application involves "multiple channels"? Are these channels connected together in some way, or do you have multiple channels that are independent of each other?

Thanks!

Brandon G

Precision DC Hardware Engineer

11-30-2012 07:30 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks, Brandon.

I am currently using a setup two paired PXI-4071 DMMs and PXI switch modules (in matrix mode) for external current measurements & an additional pair for MUX'ed voltage measurements to verify that internal meters on my equipment are performing as desired during acceptance & performance testing. The V-I results that are logged during execution of my LabVIEW program are compared with both setpoints and the results logged by the internal voltmeters and ammeters.

The current measurements need to be performed using a matrix switch because the test equipment requires a continuous current path through each DUT, or it will call that DUT "dead" and discontinue testing it. It will also call a DUT "dead" if a shift in resistance above a certain threshold is detected. I have taken care, therefore to design an external resistor that "looks like" the internal shunt resistor of the DMM. The matrix switches this resistor in and out of the continuous current path depending on whether the DMM is taking a measurement or not. Because the equipment was not designed for this type of external monitoring, triggering is not a feasible option for synchronizing external and internal measurements, so the external "shunt" resistor becomes critical to ensure that the populations of the current measurements can be considered comparable.

The number of sources I can monitor during any given data acquisition "run" is limited by the size of the matrix accommodated by the switch modules. I am presently using PXI-2530's with 2632 terminal blocks that are configured for an 8X16 matrix. I use one row for each DUTs current return path from the DMM, and two columns for each DUTs current supply path -one with the external "shunt" resistor and one without. When current is not being measured, the crosspoint corresponding to the DUTs return row and its shunt supply column is closed. To measure current, crosspoints to connect a dedicated "read" row to the non-shunted current supply path and the DMM+ terminal (which takes up one column) and the DUT's return row is connected to the DMM- terminal (which takes up another column). In this way, the 8X16 matrix can measure current from 7 sources, for a total of 14.

I am looking at ways of increasing the number of sources I can monitor during a "run," but want to reduce the cost if possible (who doesn't?). When I originally posted the question, I was looking for ways to use three matrix modules to switch current and still measure voltage. But I only have three PXI DMMs. I recalled having seen the thread I linked to, so sought clarification. What I learned is very interesting, as I potentially would not have to use two columns for every row, which opens up my options to have a square matrix and FURTHER increase the number of sources I can test should we opt to purchase a Switch Block with the 16X22 cards.

I would replace each DMM with a channel of the 4-channel SMU. That's a very long-winded explanation how "multiple channels" come into play.

11-30-2012 09:55 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Jeffrey,

Note that the four 4141 channels share a common LO terminal... I don't know if this is an issue in your setup, but now you know :).

As Brandon mentioned, the voltage across the 4141 will be close to 0; at peak current - 100mA - the 4141 develops less than 5mV burden voltage when set to 0V... the drop across your switch matrix is likely higher, depending on your test current.

You mention that your DUT must maintain a particular resistance, and that you've created a dummy resistance to mimic the DMM's shunt resistor... I'm having a hard time visualizing how you've routed these connections through your matrix... can you give us a summary diagram of maybe two of your DUTs and how they interact with the matrix? If all the DUTs share a common ground or power tap, then we might be able to get rid of the matrix and use a mux or two instead (by connecting multiple relays at once). Without a diagram, I trust your judgment using a matrix, but I'm always looking to optimize :).

Problem Solver

12-01-2012 06:38 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi, John. Not sure i understand what you mean by the statement that the four channels share a common LO terminal. The pinout includes separate "LO" and "LO S" connections for the low-side of each channel's force and sense. Are you saying that these are connected internally to the module somehow?

My current levels are going to be in the vicinity of one microamp. Are you able to guestimate the burden voltage that might result? I do plan to compare using the 4071 and the 4141 modules to measure currents early next week.

As I am using reed switches, there is some thermal EMF generated. When I worked out the polarities of the various switches that are actuated in 2 wire multiplexer mode, I identified that the thermal EMF canceled out for all but one switch. I should repeat this for a matrix configuration.

As I am on my home computer right now, I do not have access to some shematics of my setup. But I can post a few when I get back to work next week. I will aim to capture images of the Soft Front Panel with my external shunt resistor connected and with the ammeter connected.

When I developed the scheme I am using, I did a lot of brainstorming to identify the simplest way to meet the requirements. I explored the use of a SPDT MUX- but I determined that I would need one SPDT MUX to maintain a continuous current path for each DUT and a SPST MUX to multiplex the ammeter to the SPDT MUX channels. In my application, I am measuring the current supplied to independent test sockets and the voltage across them. And the test setup needs to operate unbeknownst to the system to which it is connected. I would love to see alternatative approaches!

Jeff

12-03-2012 11:16 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Assuming nobody lost any sleep since Saturday because of all of the suspense..... Here are the images!!!

Wiring goes like this:

r0: No connection

rX: Channel X current return to DUT circuit.

c0: DVM- terminal

c1: DVM+ terminal

c(2X): Channel X current supply from DUT circuit

c(2X+1): Channel X current supply from DUT circuit thru external shunt resistor

I've shown the "bypass" switching configuration I use and the switching configuration for measuring current on the first two channels. The others follow the same pattern moving across/down the matrix.

Jeff

12-03-2012 07:16 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Jeff,

Thanks for sharing the diagram with us. I think I understand this much better now. The pinouts for the front-end connector do have separate paths for each Lo but the 414x SMUs have these all these connected together internally. The Sense LO leads however are separated out per channel allowing for differential measurement remotely thru the sense leads.

Regarding the voltage drop when using the SMU, there are a combination of factors (some already discussed) that will affect how much voltage drop will be seen in the system overall, including:

1. Thermal EMF

The thermal EMF for the 2530 is spec'd at < 50 uV in 1-wire mode, however this should be less in 2-wire mode as the much of the EMF from one wire is cancelled out by the other wire. Did you have a chance to look at the thermal EMFs in the matrix configuration yet? I would expect this to be much smaller than 50 uV but if you have some measurements, please feel free to share them with us.

2. I*R drops in cabling and switches

The resistance from channel to column is spec'd at <2 ohms. Since the SMU would be taking up two columns, I would double the resistance to 4 and then conservatively estimate the total wire resistance to be 6 ohms, giving us a total of 10 ohms, conservatively. At 10 uA, we have the potential of 100 uV of voltage drop.

3. Offset output/measurement accuracy of SMU itself

For the 4141, this is spec'd at +/- 600 uV when self-cal has been performed in the last 24 hours, and the temperature hasn't changed more than +/- 5 C from self-cal; the 4140 is spec'd at +/- 5 mV when using the same time and temperature conditions. The 4141 only, has a +/- 1 degree spec of +/-150 uV, which is the offset accuracy I mentioned in my previous post. You can look at the section titled, Voltage Programming and Measurements Accuracy/Resolution in the spec for more information there.

4, SMU voltage load regulation

Voltage load regulation tells us how much the output voltage will change based on the output current of the SMU when in local sense. The spec for the 4140/4141 is 10 uV per mA of output current, so therefore, this is negligible when we're talking 10 uA or less (< ~100 nV)

Based on these numbers I provided above, we're looking at a conservative estimated system burden voltage upward of +/-300uV for the 4141 and +/- 5.15 mV for the 4140 when sourcing 10 uA. I'd expect these numbers to be much less but this is just a first-pass estimate.

Keep in mind that the offset voltage (#3) will be the smallest right after performing self-cal, so a smaller offset error can be assumed if performing self-cal more frequently than 24 hours.

To reduce the voltage drop created by #2 and #4, you can use remote sense to compensate out the voltage drop in your wires, switches and the resistance internal to the SMU itself. This of course would require 2 extra columns and 2x number of rows to route the extra signal paths. What is the expected voltage across your DUT? Sometimes it's useful to look at the ratio of the burden voltage to the DUT voltage so see how great of an impact the burden voltage will have on the overall performance.

Do you have a target for the overall burden voltage you would like to hit? Is 300 uV or 5.15 mV too large for your application? Generally, burden voltages on DMMs will be on the order of 100 mV to 1 V, so an SMU will definitely give you an advantage in that regard. Also, another feature on the 4141 only that may be useful for your application, is that you can have a programmable output resistance. I'm not sure if this would work for your application, but I saw that you were using dummy resistors to simulate the shunt and the 4141 may be able to simplify this for you. Perhaps you could cut your column count in half by reprogramming the output resistance from 0 ohms to x ohms? Just a thought but, wanted to share with you just in case.

Let us know what you find and we'd be happy to help.

Thanks!

Brandon G

Precision DC Hardware Engineer

12-04-2012 07:00 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi, Brandon. I appreciate you detailed response, and have some further information.

1. I measured the thermal EMF of a 2-wire topology using the PXI-2530 with the 4X50-pin breakout cable and one terminal block to be on the order of 25 uV. I have not yet looked at the schematic to see how many switches are in each orientation when the PXI-2530 is used in the 8X16 matrix topology.

2. The relevant comparison for IR drops in cabling is between the circuit with the ammeter inline and the circuit in its bypass configuration. I admit that I ignored losses in cabling and switches when I determined the value of the external shunt resistor- which was intended to compensate solely for the internal shunt resistor of the DVM in the 1 mA range. The same type of wires are taking the signals between the terminal block and the DUT in either mode- so the differences are the cabling between the terminal block and DVM/SMU- I am currently using banana plug cables- which are fairly large stranded wires.

3. I currently do not have the self-cal VI in my program, but can add it if there would be benefit. My data collections runs will not take more than 24 hours each. I am not sure how accurately the temperature is controlled in the lab, but I do know it varies from area-to-area depending on how close one gets to the stress and bake ovens.

4. In the tests I have run this week, I am using remote sense (connected to HI S and LO S) with the HI and LO pins of the SMU not connected to anything. I need to think about how I would implement your suggestion of using additional rows/columns for the HI/LO- but, in addition to identifying whether the SMU can replace a DMM for my current measurements to increase capacity, I am also considering whether the SMU can eliminate the need for my external shunt resistor.

I am going to table calculations or measurements of the overall IR drop of the switch/SMU system until I have a better feeling for its capabilities.

I have run two tests, and am not yet happy with the results. I am using a constant-voltage supply to apply 1V across a 15 kOhm resistor. I am using my PXI-based system with a PXI-2530 & 8X16 matrix terminal block, a PXI-4071 DMM (as before), and a PXI-4141 SMU (HI S to LO S replacing the columns for one of my DUTs in my previous setup) to measure the following:

a. Current, using the DMM in its 1 mA range.

b. Current, using the SMU. I am also logging the voltage coming out of the NI-POWER measurement VI.

c. Current, using both the DMM and SMU in series (logging the SMU's voltage as well)

For my first test, I set the SMU to the same 1 mA range as the DMM and let the system collect data overnight. The SMU was reasonably well behaved, although more noisy than the DMM until about halfway through the test, Then there was brief burp, the results quickly returned to "normal." About 3/4 through, however, the data from the SMU got very noisy until the end of the test. Whenever the SMU current measurements spiked up, there was a corresponding drop in the measured voltage, with the measurements sometimes dropping below zero. It is possible that what I observed is a result of the stress tool taking measurements at the same time as the NI system. I saw similar artifacts in my internal stress system data when comparing it to the external NI data and will reduce the frequency of internal measurements.

For my second test, I changed the range of the SMU to be 100 uA (1V/15 kOhm = 66 uA). The results are qualitatively similar, except that the noise in the current spikes downward.

Based on the suggestion in your final paragraph, I inserted the Set Output Resistance VI in my sequence. I currently have it set to zero Ohms. Do you know if there is a minimum absolute value that it will use? The documentation only discusses a maximum absolute value based on the current range selected. I am collecting some data to sanity check this now, and will start another overnight collection run with an autozero of the SMU and infrequent internal data collections on the tester.

Thanks again!

Jeff

12-05-2012 02:02 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey Jeff,

Thanks for the added details on your setup. On your overnight test using the SMU in the 1 mA range were you also using the DMM concurrently to compare measurements between devices? The noise in the measurements will be a function of the aperture time set on the SMU and therefore you may need to increase this to reduce the measurement noise. Do you know what your aperture times were on your overnight test, both on your DMM and SMU? If the DMM is using a larger aperture time, than I would expect the noise to be smaller. Do you have graphs you can share on both the DMM and SMU so we can compare them?

If the noise is being picked up by added equipment in the room, I would recommend using twisted shielded pair wiring for your cables and terminate the shield to chassis ground on one side of the cable only. You want to terminate only one side of the shield to ground as terminating both sides can create ground current loops.

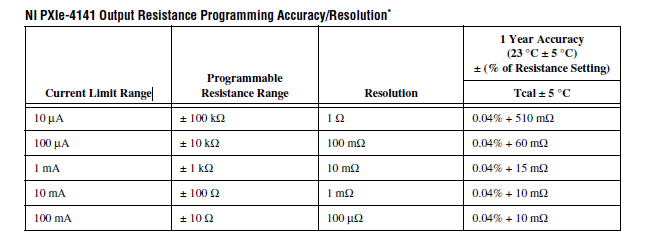

The programmable output resistance can be either + or - on the 4141 and is dependent on the range. The table below list the resistance range on the 4141 for each current range.

Please let us know what you find out about the noise in your system and we can help nail down where its coming from.

Thanks!

Brandon G

Precision DC Hardware Engineer

12-05-2012 04:51 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Ah. The Manual/Data Sheet! Too bad I didn't have the time to look there before posting yesterday afternoon!

All of my tests have collected the current measurements as determined by the DMM and the SMU with each connected independently and both in series with each other.

I did not program the SMU's aperture time until just now, when I set it to 100 ms, based on the curve on the top of page 3 of the spec manual in front of me. What is the default for the SMU? My DMM is letting the aperture time be determined by the 6.5 digit configuration I am using for the current.

I used the term "noise" loosely. It may be true noise that the instrument is picking up. What I know is that the measurement results from the SMU are more variable than desired. However, the current measurements from the DMM do not have increased variability when the SMU is in series than when it is disconnected. This indicates that there is not "noise" present, and that the aperture time may have a significant impact on my results. I will know for sure within an hour or so!

Jeff