- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

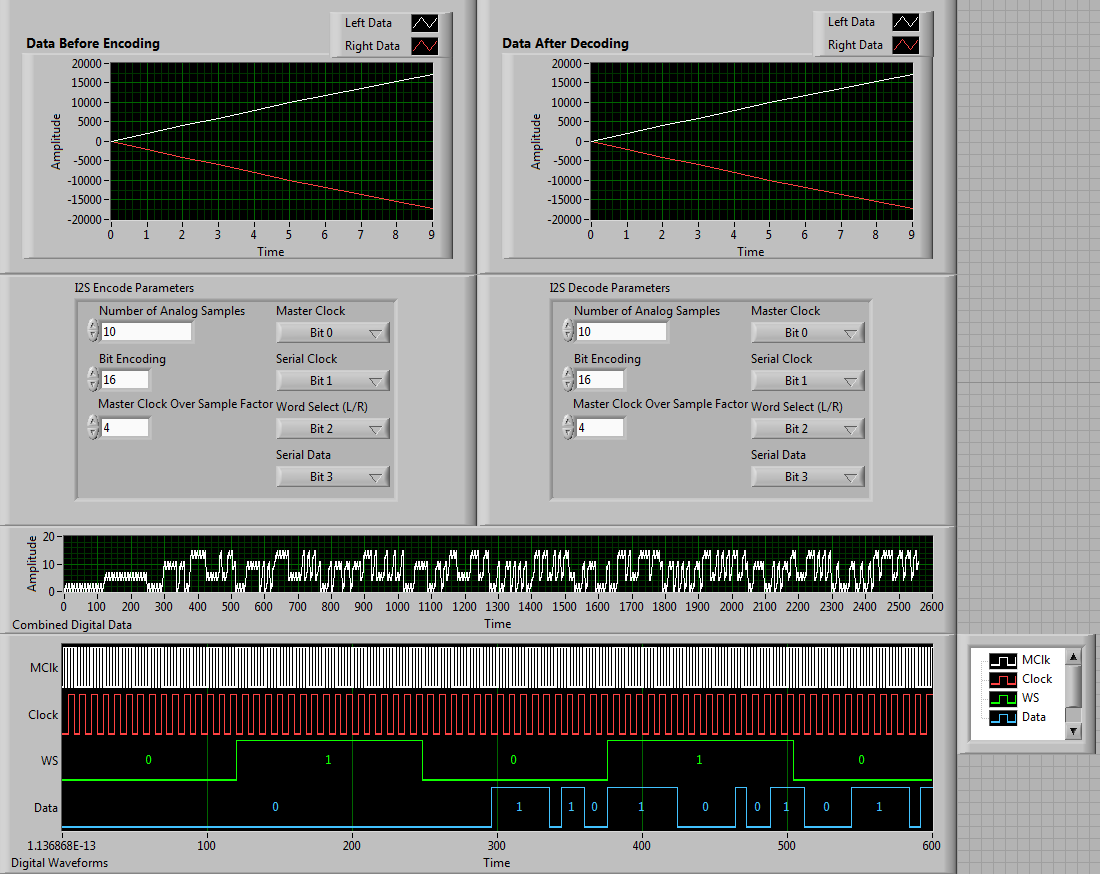

I2S: Encoding and Decoding Signals in LabVIEW

08-05-2009

03:31 PM

- last edited on

05-16-2016

09:38 AM

by

![]() Christian_L

Christian_L

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Please provide feedback, comments, and questions on various I2S examples in this thread.

Generate / Acquire I2S Signals using High Speed Dogital I/O (HSDIO): https://decibel.ni.com/content/docs/DOC-47263

I2S Decoder using LV FPGA and RIO HW: https://decibel.ni.com/content/docs/DOC-1230

05-31-2010 02:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi ninjaphil,

I am not familiar with the protocol, but just wondering if this reference design can be used with M Series Correlated DIO?

I would appreciate any advise.

Thanks.

Sincerely,

Krisna

Certified TestStand Developer (CTD)

Using LabVIEW 8.5.1 (2008) to LabVIEW 2024

05-27-2013 08:19 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The NXP info link is dead, I2SBUS.pdf is no longer on their site.

05-28-2013 01:42 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

It's only 7 pages but it is a start.

Kees

07-26-2013 06:36 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello

where can I download the vi's cited in http://www.ni.com/white-paper/9540/en (e.g. I2S_Decode_Formated_Data.viI2S_Decode_Formated_Data.vi) and also the physical connections to a DIO or FPGA board?

thanks in advance.

Giovanni

08-20-2014 07:35 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'm pretty new in this type of protocol. I'm trying to integrate the I2S to HSDIO. May I ask what is the connections I should make (I'm having HSDIO to generate and acquire at the same time without a DUT in between). How many bits does the I2S encode output uses?

Please advice

Thanks

Warmest regards,

Lennard.C

08-21-2014 12:29 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

In general I2S includes 3 signal lines. This I2S description should povide you most of the necessary information. I assume you will generate and read back the I2S bus, you will use 6 pins/channels in total, 3 out and 3 in.

https://www.sparkfun.com/datasheets/BreakoutBoards/I2SBUS.pdf

08-24-2014 09:46 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Christian,

Thanks for the reply. I would like to ask if I were to use 4 channels in which consists of the Master Clock, Serial Clock, Word Select and Serial Data to the HSDIO, would it be possible to decode using the I2S decode portion from the example? If so, what are the changes (e.g. connections from the HSDIO or the code) I need to take note of? Can this I2S encode and decode subVIs can be used for general I2S encode and decode applications? What defines the value for "Master clock Over Sample Factor"?

I also noticed that there is a CLK IN/OUT function for the Master Clock however they are not enquiring external CLK in/out ports of the HSDIO.

Please advice

Thanks

Warmest regards,

Lennard.C

Singapore (65) 6226 5886 | Malaysia (60) 3 7948 2000 | Thailand (66) 2 298 4800

Philippines (63) 2 659 1722 | Vietnam (84) 28 3911 3150 | Indonesia (62) 21 2783 2355

08-26-2014 01:34 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Yes, If you have those four incoming signals you can pass them to the I2S_Decode function.

The array going into this VI must contain the combined data from the four signal lines in each element of the numeric array. i.e. each bit of the numeric value represents one digital line. Since you only have four digital lines the numeric values should be in the range of 0 -15. I have attahced an updated VI that shows the combined digital data and separate digital waveforms. Your data coming from the HSDIO should look similar to the combined digital data array.

The Master Clock Oversampling Factor represents the ratio between the Master Clock frequency and Serial Clock frequency. If they are the same it should be 1. In my example I used a factor of 4 so the MClk is four times faster than the serial clock. The serial clock corresponds to the updates of the Data line containing the analog values.

09-11-2014 09:31 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Have you decoded and listened to any audio using this VI? I am just wondering what the quality of the data would be once it has been decoded and processed, any additional noise or distortion for example.

Thanks