- Document History

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report to a Moderator

myPID with myVTOL miniSystem

Description:

This example takes advantage of the PID Express VI for LabVIEW FPGA to control the miniSystem myVTOL, which originally was released for the NI myDAQ. The superior RIO architecture on the myRIO allows us to have much faster control systems then using the myDAQ, since the control actually operates on the realtime system instead of a computer attached to the myDAQ!

Instructions on how to use Code:

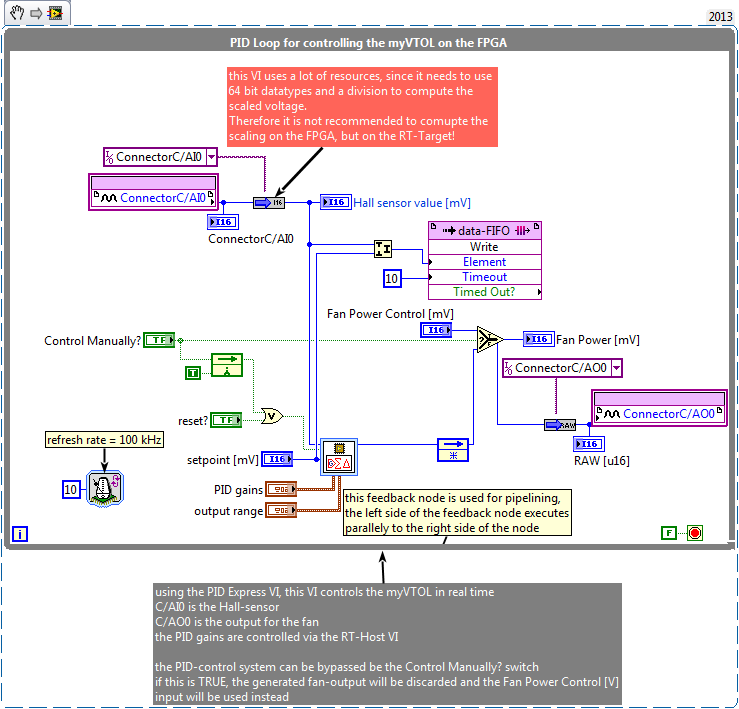

Just open the RT-Host.vi from the Project Explorer. This VI will call the FPGA VIs, which actually runs the PID control with 10 kHz. In order to display the data of the setpoint and the current Hall sensor value, a FIFO is used, so the RT-VI can actually see all the captured data on the FPGA. The controls and indicators on the left accessing the FPGA via Read/Write controls.

I have not approved working GAINS for the PID yet.

FPGA code

The user input and hardware control is built around the PID express VI. To display the measured values in readable values of mV, a scaling has to be performed. This should rather be done on the RT controller, but for the sake of showing how it would work on the FPGA, I implemented it this way!

Note the blue feedback node, which is used for pipelining the FPGA code! This is a usefull practice to fit more code on an FPGA and shorten the longest/critical path! (learn more about pipelining here)

This example does not use the shipped FPGA-personality. Any In and Outputs have to be accessed through the FPGA, the RT VIs of the myRIO palette will not work!

The ZIP file contains bitfiles as well, so you don't have to recompile!

Product Marketing Manager for CompactRIO & TSN

Making the intangible, tangible