- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA: viewing internal signals in ModelSim

Solved!04-07-2014 10:21 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have a piece of FPGA code written in LabVIEW that I'm trying to simulate in ModelSim. I followed the instructions provided in this link, but the example is a simple incrementer with no internal signals (only the input and output).

I created a testbench and succesfully started the simulation, but the provided .do macro only adds the inputs and outputs to the wave window. ModelSIM lists pages and pages of processes and signals that can be added to the waveform window; all have completely opaque names. I found something called "TheWindow", and then a subdirectory called "TheVI", and added all those signals to the waveform window. The names are things like ResHolder00000000000001 and provide no information on where they came from.

I tried assigning labels to the wires of my LabVIEW block diagram, but that didn't help at all in creating useful names. I need to check the progression of states in my VI but can't find anything that seems to resemble the appropriate signal. Many of the waveforms available under "TheVI" are static waveforms, uninitialized, or both. How can I assign useful names for internal signals so that the waveforms are actually intelligible?

On a side note, this is also a problem in the synthesizer. I am used to using synthesizer output to "pre-debug" my code, but LabVIEW seems to skip the whole macro inference process. I tried putting a SCTL with an incrementer, and LabVIEW didn't infer a counter. I have never seen one of my state machines recognized in the synthesizer even though the code works properly.

Using ModelSim PE 10.3, which I understand is not "officially supported", but the fact that the synthesizer and the simulator have the same naming problem makes me want to eliminate this as a problem. I'm not using any of the PE extensions over the SE version.

Solved! Go to Solution.

04-08-2014 03:38 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The easiest way to see the internal signals you are interested in is to create a indicator for them. This will force the simulator to track them with the name you provide. Once you are finished debugging, the extra indicators can simply be removed.

National Instruments

04-09-2014 08:41 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have a state machine with 12 states, and each state has multiple decision/calculation nodes. 50 indicators would be a little prohibitive. While I certainly wouldn't need to see every one, the nature of troubleshooting means I may not know which one I need until after the fact. I don't need to know any of the encrypted LabVIEW proprietary logic signals -- just the signals and nodes I define in my own code.

04-09-2014 08:52 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Nick,

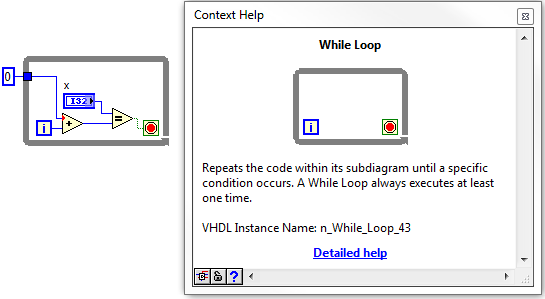

While it's not the most readable, its not too hard to find the signals that you're looking for. Your biggest help is going to be the context help in LabVIEW. If you hover over any of the structures, nodes, or wires in your LabVIEW FPGA design, at the bottom of the context help window, you'll see something called "VHDL Instance Name".

Once you navigate in the heirarchy down through the Window, into the VI, you should start seeing some of your top level items, like while loops etc. From here, you can navigate down into whatever level, and find the wire you're looking for.

I don't have ModelSIM on my machine, but this works for ISIM. I wish they had a search feature so you could just type in the signal that you're looking for.

TJ G

04-10-2014 10:34 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks, that's it! In a very intuitive place, too. Looks like I need to get my eyes checked.