- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Abnormal behavior of Analog output on FPGA

Solved!10-29-2021 07:04 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

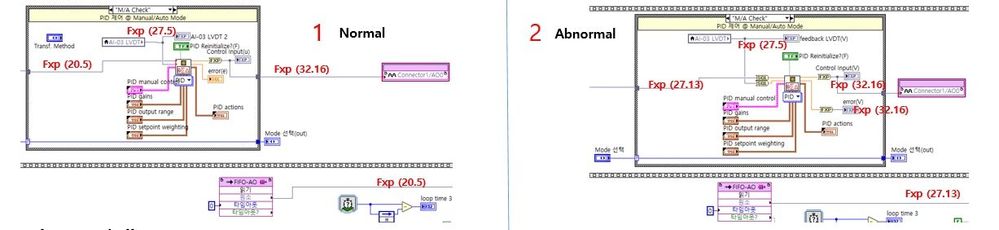

The PID control logic was configured by using the FIFO of the FPGA module.

For the same host vi,

FPGA code 1 works normally and FPGA code 2 is abnormal.

Abnormal phenomena are as follows.

After the initial compile, the FPGA itself works normally,

but when Host vi is started, AO stops until the computer is rebooted.

What causes these problems to occur?

For reference, fxp data type is indicated in the attached figure.

The difference is only fxp data type.

Solved! Go to Solution.

10-29-2021 08:55 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

My problem was not at all with fxp data type.

It was just a problem caused by setting the value setting of output setting, which is related with an input parameter of PID.

Thank you for your interest.

I feel deeply that i should always stick to the basic.