Discusiones sobre Productos NI

- Suscribirse a un feed RSS

- Marcar tema como nuevo

- Marcar tema como leído

- Colocar este tema arriba del foro

- Favorito

- Suscribir

- Silenciar

- Página de impresión sencilla

- « Anterior

- Siguiente »

problema al adquirir señales analógicas

el 04-23-2015 06:11 AM

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

Buenas,

Estoy intententado adquirir señales analógicas con el módulo 9205 y el cRIO 9067. Para ello he creado un proyecto donde la FPGA se encarga de adquirir esas señales, que son una misma señal de una tensión conectada a varias entradas, y guardar dichas señales en un buffer FIFO para después representarlas en una gráfica a través del cRIO.

El VI de la FPGA tiene un bucle While que contiene un Flat Sequence Structure con tres secuencias donde hay:

- Un Loop Timer a 200usec

- Un FPGA I/O Node con las entradas del módulo 9205

- Un Build Array con todas las señales conectado a un bucle For que contiene un FIFO.

El VI del cRIO abre el VI de la FPGA y está conectado a un Invoke Method en modo Run conectado a un bucle While que contiene:

- Otro Invoke Method que lee los datos del FIFO de la FPGA

- Decimate 1D Array conectado a las gráficas que quiero representar.

- Un Wait(ms) a 100ms

Y fuera del bucle For cierro el VI de la FPGA.

Consigo representar las gráficas pero el problema que tengo es que no son senoidales puras, aunque casi, y muestran desfase entre ellas. ¿Alguien me puede ayudar?

Saludos

el 04-24-2015 06:56 AM

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

Hola c.ales,

tal y como lo describes parece que el desarrollo es correcto. No obstante, sería de ayuda que pusieses el código para poder ver dónde está el problema.

Saludos!

Jesús

el 04-27-2015 01:09 AM

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

Hola c.ales,

¿lo has podido resolver ya? Haznos saber.

Saludos!

Jesús

el 04-27-2015 02:01 AM

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

Buenas Jesús,

No, aún no he logrado resolver mi problema.

Adjunto el código a ver si alguno me podéis ayudar. Gracias

Saludos

el 04-28-2015 01:43 AM

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

Hola c.ales,

el código, salvo algún pequeño detalle, está bien a grandes rasgos. Para trazar bien el problema, mi recomendación es que, en lugar de utilizar todas las señales del módulo, utilices sólo un par de canales. ¿Se sigue produciendo el error con sólo dos canales?

Hazme saber, por favor.

Saludos!

Jesús

el 04-28-2015 01:49 AM

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

Por otra parte, como puedes ver en la pagina 9 del manual del 9205:

http://www.ni.com/pdf/manuals/374188d.pdf

los canales de entrada son multiplexados, esto es, hay un delay o retardo entre la adquisición de una señal y la siguiente. Puedes estimar el interchannel delay con el siguiente documento:

http://digital.ni.com/public.nsf/websearch/9AE87416C8792FC286256D190058C7D3?OpenDocument

¿Qué delay estás viendo entre canales?

Jesús

el 04-28-2015 01:56 AM

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

También sería muy bueno probar con un módulo que no esté multiplexado y que tenga, en lugar de multiplexor + ADC, un ADC por canal. En este caso, las señales se muestrean de forma simulatenea real. Ejemplos de módulos de adquisición simultánea no multiplexada son los siguientes:

http://sine.ni.com/nips/cds/view/p/lang/es/nid/210836

http://sine.ni.com/nips/cds/view/p/lang/es/nid/212730

¿Dispones de alguno de estos dos módulos o algún otro parecido para poder hacer la prueba?

Saludos,

Jesús

el 04-28-2015 04:02 AM

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

Hola JesúsG,

Ante todo muchas gracias por tu contestación.

Le he quitado entradas y sólo he puesto 7, 6 de ellas están adquiriendo una señal de tensión y otra está conectada al COM.

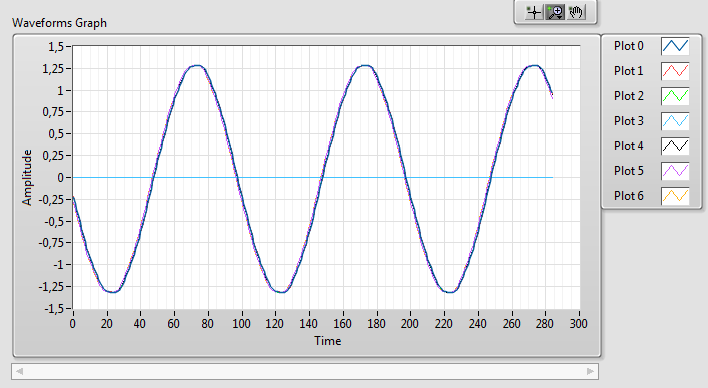

Esta es la gráfica con las señales que estoy adquiriendo.

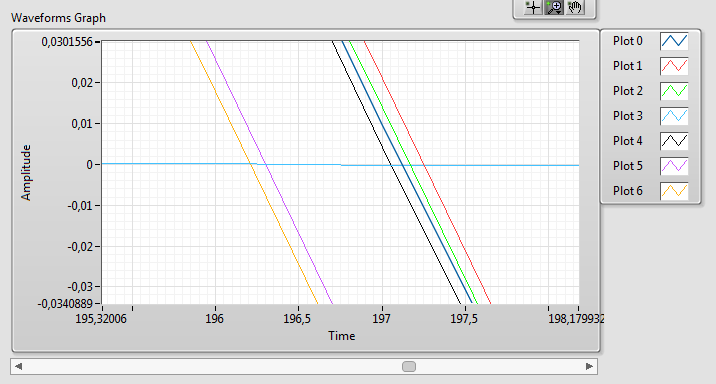

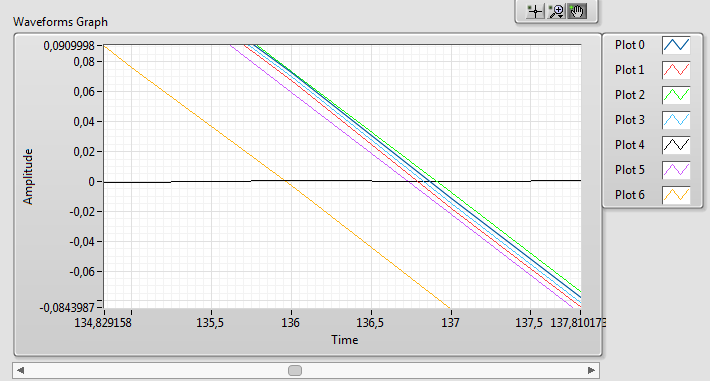

Si pauso la compilación y hago zoom obtengo esto

Como puedes observar en las imágenes hay un retardo entre señales, así que no creo que sea debido al número de canales, pero sigo sin saber cuál es el problema.

También me he fijado que depende de cuando pause la compilación cambia la señal que está a 0 y el retardo entre señales también varía.

¿Sabes a qué se puede deber?

Saludos

el 04-28-2015 04:05 AM

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

Sí, sé que hay un retardo entre adquisiciones, pero creo que no me debería de afectar tanto como se muestra en las capturas.

el 04-28-2015 04:05 AM

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

No, sólo dispongo de este módulo para hacer pruebas.

Saludos

- « Anterior

- Siguiente »