- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

NI 9361 Counter Timeout?

06-15-2017 10:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

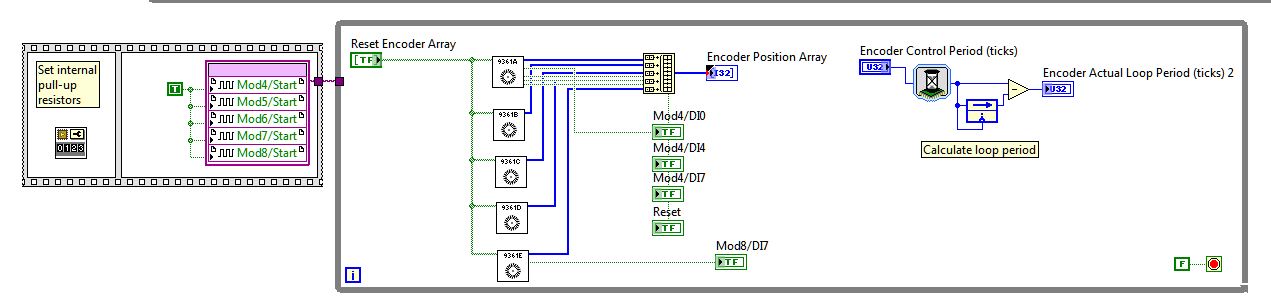

I'm having some unusual issues with my FPGA code using 9361 counter modules to count encoder pulses.

My 9068 cRIO has 5 9361 modules that read pulses inside a single loop in the FPGA code. There is also a 9205 and 2 9264 analog cards that operate inside of a separate loop on the FPGA.

It seems that occasionally the loop with the counter modules is hanging on something or just not running, as the reported tick count for that loop falls to 0 and encoder pulses no longer make it back to the UI.

Running the FPGA panel in interactive mode confirms no pulses are being counted.

Is it possible that I need some wait time between setting the pull-up resistors and starting the module?

It seems like it might be the "soft" reset that happens on connection that might be hanging the loop. As it seems to occur when the RT/UI disconnects and then reconnects.

Any suggestions would be most welcome!

06-16-2017 01:11 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Has the hanging always occurred? Also can you successfully run the code in Simulation Mode?

06-16-2017 02:34 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I would say that the hanging has always occurred with this code. I've not yet tried to run the code in simulation mode.

06-19-2017 01:42 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

What's in the 9361 subVI? I'm assuming you don't have a loop in there that could hang? You might want to give each module its own loop. It would isolate if there's any one module giving you trouble.

06-19-2017 02:25 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Your code looks fine. You shouldn't have to include a wait time between the pull-up resistors and starting the module, as long as the pull-up resistors are configured correctly.

Perhaps this is a networking issue between the HMI and RT Target. Have you tried writing/reading to a network-published shared variable instead?

06-19-2017 05:43 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The "fix" for now is to change the Close FPGA References blocks in the RT code from the default behavior that is Close and Reset, to just Close.

After that change, I haven't had the Encoder loop hang up again.