- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

triggering FPGA acquisition loop

04-22-2016 09:40 AM - edited 04-22-2016 09:49 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi everyone,

I am not very experienced with Labview FPGA, and I am stumped with this task. Here it is:

I want to generate a function with a PXI 5402 function gen, and trigger an FPGA acquisition loop each time the function is generated in order to perform repeated measurements on a flexRIO 7962R with the 5752 acquisition module.

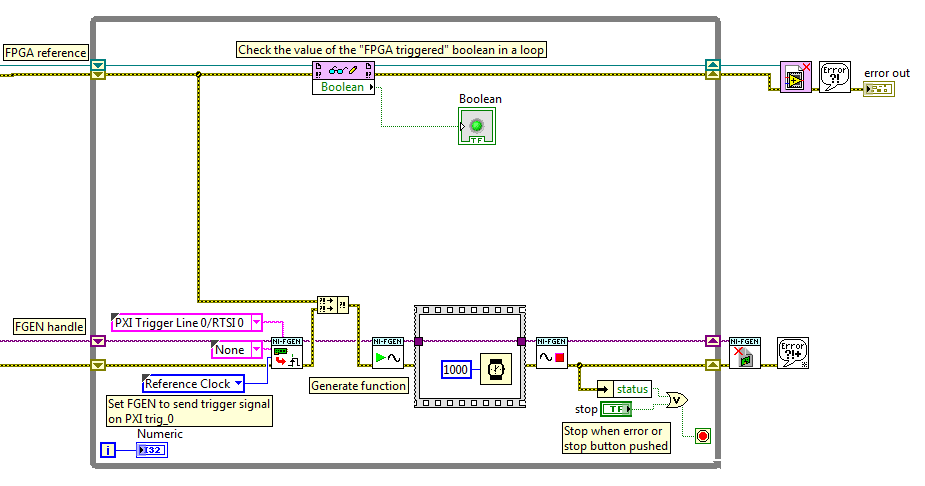

So far to keep it simple I am just testing the triggering part using the PXI_trig0 line, and trying to tell whether the FPGA triggers properly. My current code, attached, is based on the "NI 5752 finite acquisition with external clock" example, modified to have the FGEN running in parallel. When I run the VI, the boolean is only true, corresponding to an FPGA triggering, for the first loop count.

I am afraid I am not checking the triggering properly, and timing issues are the source of this behavior, but I don't know of a better way.

Could someone point me towards a better way to do/check my triggering, so that I can make sure the FPGA triggers before working on the data acquisition and transfer part of the project?

Thanks in advance,

blum22

04-22-2016 12:35 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Could you try attaching the FPGA portion of the project again, I don't think that it was included in the attached zip.

04-25-2016 08:00 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Matt,

Here is the full project with the FPGA vi , I apologize for the mix-up.

blum22

04-27-2016 09:01 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Would screenshots help? Here is the triggering loop part of the host VI, as well as the FPGA VI.

Any help is greatly appreciated!

blum22