- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

schedule FPGA action in case of loss/problem on communication

Solved!02-17-2023 07:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have a NI9074 cRIO with 3 NI9485 with whom I control some electrovales to fill a tank of diffenet gases, at differente pressureand tempoerature, and 1 NI9219 to read the temperature and teh presuure inside the tank

I have already developed a program that which allows the tank to be filled at the deiserate conditions, but some during the test, expecially if the test is very long (several days) I have run into several errors related to the loss of communication between my cRIO and the PC.

This led to loss of control over the gas input and having too high pressures or temperatures inside the tank.

Although there are safety valves , I would like to implement a program in the FPGA of the cRIO that, in case of loss of communication will close all solenoid valves and turn off the heaters aslo if the pc crashed, or in case of some communication problem.

I am enclosing a test of code that I have started to make, but it doesen't work, infact if I disconnect the LAN cable ( which connects the PC with the cRIO), or if I switch off the pc, to simulate the communication lost/problemI do not achieve the desired effect, which would be to close all the solenoid valves( trough NI9485).

Can some one help me?

regards

David

Solved! Go to Solution.

02-17-2023 12:00 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Your top-level code (UI Main) looks like an NI Example, one with which I'm not familiar (I also find them overly complex). I mention it because I don't see a similar routine on the RT side, but never mind ...

You want something called a "WatchDog Timer". The notion is that the FPGA runs a timer that, say, counts seconds, and if it ever reaches 1000 seconds (or whatever "Time-out" time you want), it assumes "Oops, something has gone wrong, nobody has petted me recently, so I better shut the system down and may even turn off the cRIO". The FPGA also has a Boolean control called "Reset WatchDog Timer" that (you guessed it ...) resets the WatchDog Timer and turns itself off.

You need a routine running on the Target that "listens" for a "Reset the WatchDog" from the Host, and every time it sees it, it sets "Reset WatchDog Timer" on the FPGA. And, finally, you need a "Reset the WatchDog Timer" on the Host that signals the Target to tell the FPGA to "Reset the WatchDog Timer" on the FPGA. So if the Host gets hung up, it doesn't tell the Target to reset the WatchDog. If the Target gets hung up (or simply stops), it doesn't tell the FPGA to reset the WatchDog. And when the FPGA WatchDog expires, the FPGA shuts everything down.

Bob Schor

02-20-2023 06:34 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Bob,

thanks for your fast answer.

About the UI Main you are rigth is an NI Example and I forgot to delete it, the code done by me are Untitled 4.vi and Untitled5.vi.

Anyway I understand what you mean, but I tried to find this Boolean control called "Reset WatchDog Timer" but I dien't find it.

Can you send me, or said where i can find, an example of watchdog on FPGA?

David

02-20-2023 06:44 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi David,

@David15 wrote:

Anyway I understand what you mean, but I tried to find this Boolean control called "Reset WatchDog Timer" but I dien't find it.

You can use any boolean control and just label it as needed…

@David15 wrote:

Can you send me, or said where i can find, an example of watchdog on FPGA?

You create you own ElapsedTime routine in the FPGA!

Whenever the RT host changes a control in the FPGA frontpanel (aka "petting") the timer is reset.

When the ElapsedTime value hits a limit (because of no RT host communication aka "petting") you start your Safety actions…

02-20-2023 07:03 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

There is a shipping example

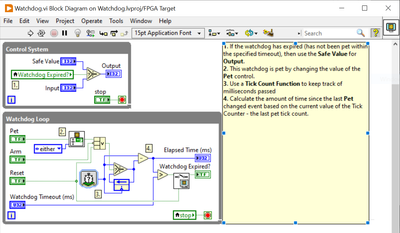

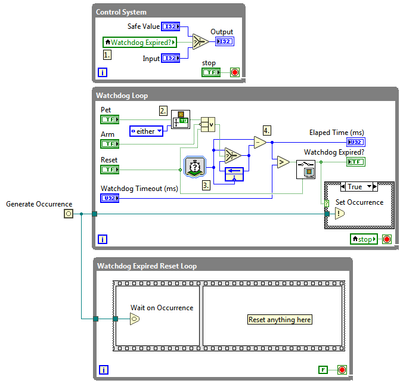

<LabVIEW>\examples\R Series\FPGA Fundamentals\Fail-Safe Design\Watchdog\Watchdog.vi

You might need to install NI R Series Multifunction RIO driver.

Applications Engineer | TME Systems

https://tmesystems.net/

-------------------------------------------------------

https://github.com/ZhiYang-Ong

02-20-2023 07:24 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I already Installed it...but in the palette i didn't find any "watchdog" vi's

02-20-2023 07:25 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Sorry but I don't understand howa simple boolean control can be used as a watchdog

02-20-2023 08:22 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

There is no FPGA API for watchdog. The example implements the watchdog using a timer and a boolean control.

Did you open and check out the example?

Applications Engineer | TME Systems

https://tmesystems.net/

-------------------------------------------------------

https://github.com/ZhiYang-Ong

02-22-2023 02:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

I saw this example, and I'm trying to understand how to use it for my purpose.

02-22-2023 08:11 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You can combine with the occurrence to trigger the reset event if the watchdog expires.

Applications Engineer | TME Systems

https://tmesystems.net/

-------------------------------------------------------

https://github.com/ZhiYang-Ong