- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

how to prevent automatic insertion of synchronization registers in LabVIEW FPGA?

Solved!02-20-2018 04:11 AM - edited 02-20-2018 04:28 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

my hardware is a FlexRIO 7962R card and a NI6581B adapter module.

On the FPGA a custom made CLIP is running using 2 different clock domains (100MHz and 25MHz). The toplevel clock of the LabVIEW FPGA VI is 40MHz.

The I/O nodes of the CLIP shall have a straight connection to the I/O nodes of the adapter module. When synthesis is finished, I'm always getting timing violations and it looks like LabVIEW FPGA automatically inserts synchronization registers between the CLIP I/O nodes and the adapter module I/O nodes that are causing those violations. The connections between the CLIP and the adapter module are made in the wiring diagram of the LabVIEW FPGA VI (it's a wire from the adapter module I/O node to the CLIP I/O node, enclosed by a while loop).

How do I disable the timing between the CLIP and the adapter module (similar to set_false_path -from CLIP -to adapterModule)? The signals that are read/written from/to the adapter module are asynchronous. The CLIP is taking care of proper synchronization of those signals.

Thanks for any advice.

Regards,

Ralf

Solved! Go to Solution.

- Tags:

- fpga

02-20-2018 05:54 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Using a Single Cycle Timed Loop is the only way I know of.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

02-20-2018 02:22 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

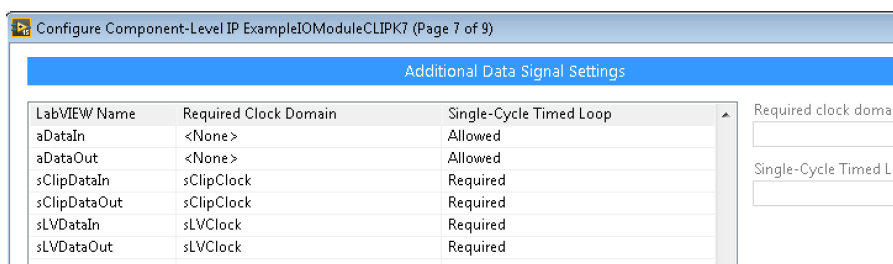

LabVIEW FPGA automatically adds synchronization registers to safe guard against metastability unless the CLIP IO has been explicitly marked as 'Required' under single cycle timed loop. This tells LVFPGA that the IO is sychronous to a specified clock and that it is safe to remove the sync registers.

I can see from your post history that you've posted in the private FlexRIOMDK forum, which tells me you have access to the FlexRIO MDK. You should take a look at chapter 13 of the FlexRIO MDK which discusses how to create a CLIP with synchronous signals rather than asynchronous signals.

02-26-2018 05:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Have you tried right.clicking ont he properties of the CLIP I/O node in question from within the Project and setting the synchronising registers setting there? We had to do that as our CLIP also exposes BRAM directly in this way. LV 2015, Virtex 5 Target.

02-26-2018 06:02 AM - edited 02-26-2018 06:02 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@Intaris wrote:

Have you tried right.clicking ont he properties of the CLIP I/O node in question from within the Project and setting the synchronising registers setting there? We had to do that as our CLIP also exposes BRAM directly in this way. LV 2015, Virtex 5 Target.

Yes, I did. But it didn't solve the issue. The solution was to replace the while loop by a SCTL.

Thanks for your suggestions.