- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

flexrio FPGA dma and dram simulation

03-06-2015 10:07 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have a pair of Flex RIO 7966r boards where I am trying to perform DRAM to DMA transfers. Each FPGA uses both banks of DRAM. One bank for capturing Camera Link frames, the other bank for capturing sub-frames from within each frame (And performing some processing on the sub-frame data).

Each DRAM bank is written into from their own target scopes FIFOs.

Each DRAM bank is read into their own target-to-host DMA FIFOs.

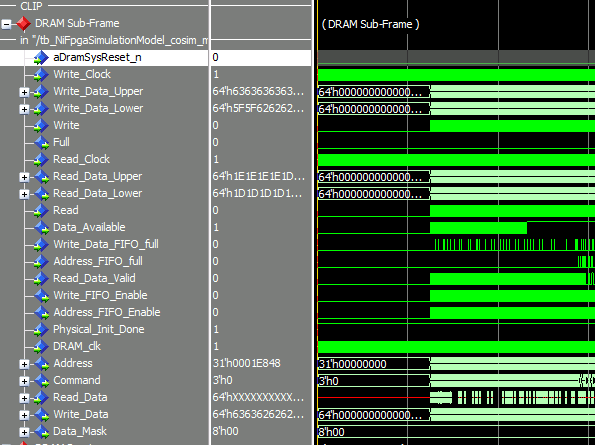

When only one side is operating or the other (Capturing sub-frames by themselves or full frames by themselves) everything flows nicely. But when I capture both at the same time, there appears to be some sort of contention in the DRAM (I suspect from the DMA engine). Since I am simulating all of this, I would like to ask if anyone has the detailed descriptions of the DRAM interface signals below? These are generated by LabView but I have found no explanation of what they mean in any documentation.

Also, in the simulation build, there is obviously a DMA simulation. But from within the simulator, I can find no signals related to the FPGA based DMA FIFOs or the simulated DMA transfers. All I can infer about the DMA transfers is the effect on the DRAM above. The DMA FIFO is being populated directly from the DRAM (Yes, this is a highly modified variant of the 10 tap cameralink (with DRAM) example from the NI-1483 examples).

Does anyone know how I can see the DMA bahavior from within a simulation? This would most likely allow me to see exactly why the contention is taking place.

Thanks!

03-09-2015 06:35 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey xl600,

I'm not immediately sure how to have ISim display the DMA Engine behavior, but I'll see if I can I dig anything up for you. I've come across a couple of other users encountering issues with FIFO signals appearing in ISim over on the Xilinx forums, so it might be worthwhile to post there as well in case it happens to be due to ISim itself.

Regards,

Ryan

CLA

03-10-2015 08:46 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'm not using iSim. I'm using Questa. But the issue is the same. Hoping to get a way to see the DMA FIFO signals.

Thanks