- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

cRIO - Troubleshooting creation and deployment of startup standalone real time application

Solved!04-18-2012 10:14 AM - edited 04-18-2012 10:18 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I am using cRIO-9024 with a 9112 chassis to control a system. I'm using LV2011 SP1. When running the system in development mode (pressing the run button), everything seems to work fine. When building the standalone real time application and running it as startup, something stops working.

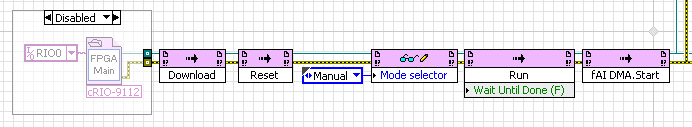

In order to know if the application is running or not, I toggle the user LED on the cRIO using this code:

When I disable all of the code in the main VI except this loop, the application deploys and runs on startup without problem (LED blinks). I then gradually add more and more of the loops that I want to run (by disabling less and less code) and the problem seems to be in the FPGA Open VI Reference block. If I disable this block, the standalone real time application runs (I guess that error -63195, invalid device communication handle, will be propagating along the line, but I know that the app is running since the LED is blinking).

I've tried several configurations for this FPGA Open VI Reference block and had mixed results. For example, if I configure it this way:

The startup standalone real time application runs with the FPGA Open VI Reference block enabled but stops working as soon as I enable some code that makes use of that reference within subVIs :(.

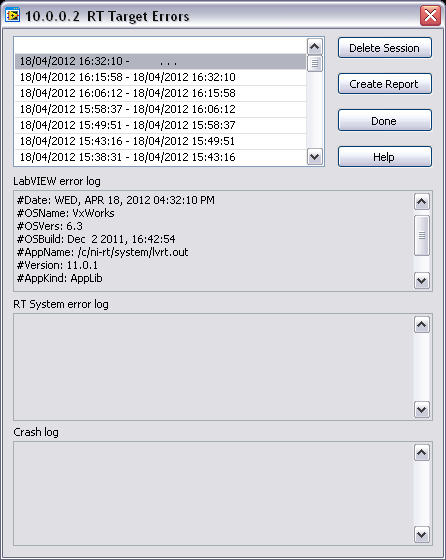

Has anybody any idea what might be going wrong? I've explored the messages thrown out by cRIO during startup but cannot see any error messages (in fact, the console output is the same when I manage to deploy an application that runs (by disabling code). I've also tried exploring Error Logs (via right-click on target Utilities >> View Error Log) but cannot decipher any useful info from them.

Any ideas will be greatly appreciated.

Solved! Go to Solution.

04-18-2012 12:03 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

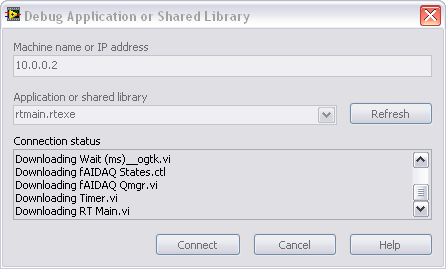

In your build, if you go to the advanced and check of the box for "enable debugging", then compile and deploy your code (as startup for example), next from the project view (or main VI?), go to "operate" and choose "Debug application or library" or something like that.

You should get a small dialog box where you can enter the IP of your target to connect. You may need to hit refresh several times and/or wait for a rather long time. Eventually, you should see a choice of "Startup.rtexe" or something like that in the box, select it and click "connect". This should allow you to probe and troubleshoot your exe(!).

I'm not sure that will help you in this situation since you have already isolated where the error happens, but it may give you some new insight in where/why stuff breaks?

Sometimes, for odd reasons, you may have luck by deleting your FPGA reference from the block diagram and dropping a new (unconfigured) one down from the palette and then re-configuring it... If this fixes it, you may want to do a "Mass compile" on your LabVIEW folder and project folder as you may have other bad links. Again, if this fixes it (delete and recreate identical), it could have happened during a recent patch or upgrade (even from 2011 to 2011 SP1).

I hadd RT code that worked perfect in development mode but failed to run (at all) as compiled exe. I recompiled the exe and eventually found that deleting a static VI reference and a static strict vi reference and re-creating them fixed the problem. (Before deleting and re-creating these two references, I had also tried right clicking on the existing reference and re-browse to the vi on disk, but this did not help...)

Hope this helps!

-------------

CLD LabVIEW 7.1 to 2016

04-19-2012 11:10 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi QFang, thanks for your reply!

I tried what you suggested with mixed results. I still can't run the finished application as startup on the cRIO. I tried Mass Compile and got quite a lot of "bad VIs" and "insane objects". They all had to do with temporary VIs that I used through development but shouldn't be part of the final application. I'm cleaning up my project just in case and rebuilding step by step.

One thing that bugs me is the following error: when I configure the Open FPGA VI Reference to open either a Build Specification or a VI, I get "Error -61017 occurred at Open FPGA VI Reference in RT Main.vi - Possible reason(s): LabVIEW FPGA: You must recompile the VI for the selected target." I do right click >> Build on my FPGA build specification and I get the message "The bitfile is up to date with the build specification."

Previously I solved this problem by opening a bitfile instead, but I'm guessing that there might be something wrong that I should be solving instead of bypassing. Any ideas?

I recently upgraded to LabVIEW 2011 SP1, should I mass compile my LabVIEW folder? Would that be "Program Files\National Instruments\LabVIEW 2011?

04-19-2012 03:17 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

hi Raul,

with regard to your problem: ![]()

- where are you downloading bitfile from? - is it necesary as already loaded on RT chassis.

- On you reset command is there suficient time delay before next sequence execution?

- what function in the start up mode does the manual selection have?

Advise I have recieved from others is always make a start up application before you finish your development![]()

The toggling of the LED is from RT not from the FPGA.

Have you tried using the RT execution trace toolkit?

Regards

xseadog

04-20-2012 04:01 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks xseadog for your reply.

I have indeed erased the Download node since it is not needed. I think I included it at the last moment following some advice aimed at a LabVIEW 7.1 issue. I now open the reference, reset the FPGA, change the value of the Mode selector indicator ("manual" just disables some safe operation logic code on the FPGA) and then run it. Should I wait some time after reset? I guessed that the node would allow flow to continue once it was done reseting the FPGA.

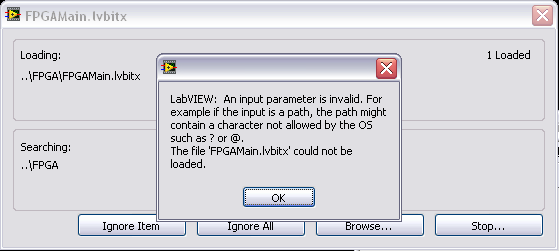

QFang, I enabled debugging and clicked on Operate >> Debug Application or Shared Library... and I got some problem that might be related to what's happening when trying to run the standalone application as startup:

I have no idea what happens when you debug an application running on a cRIO. The second dialog seems to be indicate that it's trying to load the bitfile. Why is it trying to load it where? I'm confused.

xseadog, lesson learnt: on my next project, a day will not pass without building and running the application! ![]() I've never used the RT execution trace toolkit, but I'll give it a try. I'll let you know if I make any progress.

I've never used the RT execution trace toolkit, but I'll give it a try. I'll let you know if I make any progress.

Any other ideas will still be greatly appreciated. Best regards!

--

Raúl

04-20-2012 05:44 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Raul,

use MAX to FTP that the bit file is located in the correct diectory on the RT chassis.

\ni-rt\startup\*.*

Ensure before you transfer that you have set the application to startup( when you have completed your build). This should be done after you have built the application.

PS

Before building remove the download action in the RT code and set the other mode to auto if you still have included.

When you set the application to startup the cRIO unit should reboot !

/Russell

04-20-2012 07:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hummm... I feel your pain, though its never been nearly as bad for me.

I should probably also point out that I have only ever used the remote debugger for RT code only, never for mixed RT and FPGA code, so I'm not sure why its trying to load the bitfile during the remote debug session.

You seem to have a lot of "weird" missing file errors and insanity etc. going on.. Is there anyone else with a computer where you are at that you could try and do a clean install and then do a project export/source export to move only the "live files" over to the new computer? Maybe a cleanly installed LV is what you need in the short term?

I have seen sometimes that one place LabVIEW will tell me I need to recompile, but another place it tells me the bitfile is up to date. You can still force a recompile (I think right-click on the FPGA vi in the project view, or of course, you could just nudge a front panel indicator on the FPGA vi and save it and that will force a re-compile as well.

Currently, I don't have the FPGA license anymore so I can't offer more details.

Good luck!!

-------------

CLD LabVIEW 7.1 to 2016

04-25-2012 10:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Raul,

I have a very similar problem. In my case I have a cluster in front panel which is updated with the data coming from FPGA. It works fine when I press the run button. But when I create and download the startup.exe file I see that except that part(updating the cluster values) other parts work. My hardware is cRIO-9024 with 9118 chassis and software is LV2011. Did you find a solution for your case. Thanks.

04-26-2012 06:35 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi kkguner,

My problem is that the code runs (apparently) ok when in development mode but it seems that, when deployed as a standalone real-time application, it fails to run at all. Since I haven't been able to get any error messages either through looking at the console output when rebooting my cRIO or through exploring the error logs from the project explorer, I can only guess on what's happening.

I have a feeling that QFang's suggestions go in the right direction, but I still haven't been able to pinpoint the exact cause and the proper solution of the problem.

The solution I've settled with has been to deploy my application as a source distribution with a startup VI instead of as a standalone real-time application. You might want to try out this option.

What I might try when I have some time is to cleanup my installation of LV (either by mass compiling or by reinstalling it completely). I tried a mass compile of vi.lib and I got an (un)healthy amount of insanities, bad VIs and several other unfortunate messages.

kkguner, let us know what you find out in your investigation or if any of the suggestions solves your problem.

Thanks QFang and xseadog for your help. Best regards!

--

Raúl

04-26-2012 03:27 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Raul,

Today I realized that I should not use Property Nodes or References for my clusters. Since the startup.exe has not any front panel it gives error and do not update cluster value. By means of the Labview help, I changed these into the local variables. Now my project works fine as a startup.exe I hope you find your solution too.