- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

cRIO FPGA Voltage Input/Output modules

06-04-2018 07:17 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello fellow labviewers. I am totally new in LabView and starting to be frustrated. I tried to search trough forums and examples for days, if not weeks but I wasn't able to finish my current project yet. I have got cRIO-9063 with two modules, input NI 9229 and output NI 9269. My goal is to have two synchronized modules, where NI 9229 (delta-sigma modulation) should decide sample rate. The output module should create signal (which will open tranzistors) and input module should read potential difference from sample. I would like output module to open tranzistors based on signal from .txt file. When there is 1, transistor should be opened and when there is 0, transistor should close. The input file should read analog potential difference and values write into .txt file for later analysis. To my understanding, for working with .txt file as well as creating of graphs after reading data i need to use RT mode of cRIO. I do not know if there is need to use also computer for opening of files. I also do not know how to properly synchronize these two modules. In attachement there is my current project but it is in incomplete state and there is probably a lot of mistakes. I would appreciate any help.

06-05-2018 03:22 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi colleague

Thanks for your posting your question here. Concerning your questions related to the synchronization, we have to ways to do this using the cRIO, and it will depend on how you operate your device.

- If you are working with the FPGA, when you create the I/O node and drag it down to add more channels, you will make this channels to update simultaneously, thereby synchronized.

- If you are working just with the Real-Time Target, if you put the I/O variables you want to synchronize on the same timed loop, those variables are going to be synchronized by the scan period of the RT target.

I can see that you may be frustrated about the execution of your project, that is why I highly recommend you use the NI support. Calling them you will find answers much faster and you can call them whenever you need.

06-07-2018 06:10 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you for your answer. I started from blank project again becase I got lost in my project. Thanks to your advice about synchronization, I am closer to what I want to achieve and it is much more clear now. I will keep updated this thread for others who could face similar issues as me. Thank you again.

06-13-2018 04:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

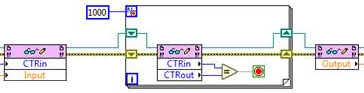

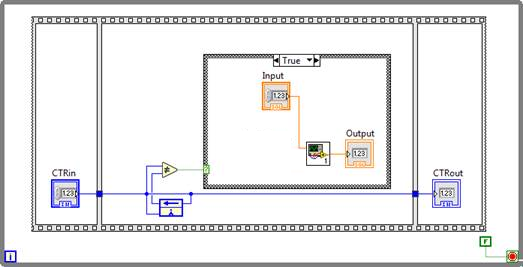

are you familiar with programmatic front panel? I used it for synchronization without being tied to the Scan Engine. open FPGA reference and use the read/write control function

RT

FPGA

06-13-2018 06:49 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Or you could use an Interrupt. With the Interrupt, your host is just waiting without burning up your CPU. It will also use less resources than the front panel controls.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

06-13-2018 06:59 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

thanks for the suggestion, will read up on that once the 81 installers are done 🙂

06-18-2018 02:31 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi crossrulz

I have read a little on the interrupt method, from:

http://digital.ni.com/public.nsf/allkb/98FCA7F87A52A14986256D280056E2B7?OpenDocument

Compared to the method I mentioned earlier, if I have a number (~256) of RT-FPGA-RT transfer to be done, wouldn't the interrupt method take longer for waiting for an interrupt and acknowledging it? And that there is no unique identifiers for the data that I sent from RT to FPGA for processing and its completion. If only RT have the "High Resolution Polling Wait VI" function...

06-18-2018 03:12 AM - edited 06-18-2018 03:15 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@cy... wrote:

Hi crossrulz

I have read a little on the interrupt method, from:

http://digital.ni.com/public.nsf/allkb/98FCA7F87A52A14986256D280056E2B7?OpenDocument

Compared to the method I mentioned earlier, if I have a number (~256) of RT-FPGA-RT transfer to be done, wouldn't the interrupt method take longer for waiting for an interrupt and acknowledging it? And that there is no unique identifiers for the data that I sent from RT to FPGA for processing and its completion. If only RT have the "High Resolution Polling Wait VI" function...

replacing the For loop with a Timed Loop (MHz w/reset), with timeout (based on iteration count) and 0<dt<100 to emulate a high resolution polling wait. what do you think of this method, possible to reduce processor load?