- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

cRIO 9049 and two NI 9215 modules sampling at 100 kHz

Solved!11-23-2018 09:52 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi All,

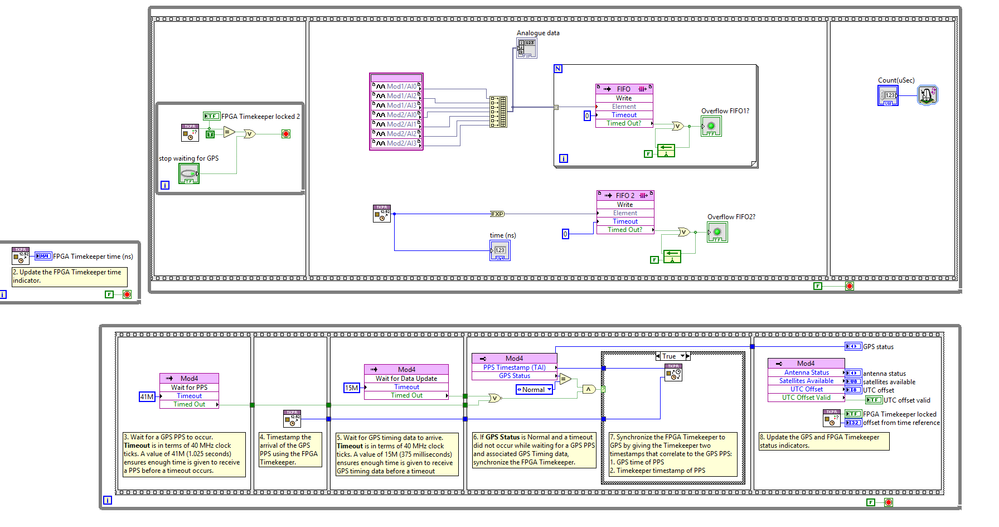

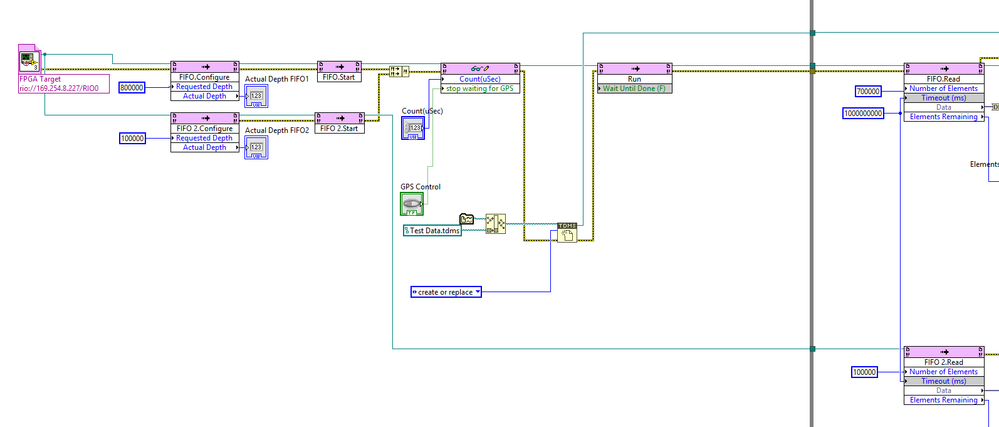

I am working on a project making use of a cRIO 9049 and two NI 9215 modules to sample eight channels at 100 kHz. I am also using the NI 9467 module to time stamp the data measurements. The analogue input channels and the time from the timekeeper are written to two separate FIFOs. These two FIFOs are picked up in the host VI where the depth is configured and then read within a while loop.

When I set the loop timer to 10 uS I can log at 100 kHz using one 9215 module, when I add the second 9215 module at the FPGA input node, the sampling rate saturates at 90.9 kHz (whilst the loop timer is still 10 uS). I have attached images of my FPGA VI (which makes use of the timekeeper VI) and my host VI. Is my general logic in the FPGA/host VIs correct? Can anyone suggest a reason/solution for the reduction in the sampling rate when gathering data from two 9215 modules on the cRIO?

Best Regards,

Eddie

Solved! Go to Solution.

11-26-2018 01:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

11-26-2018 05:37 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi GerdW,

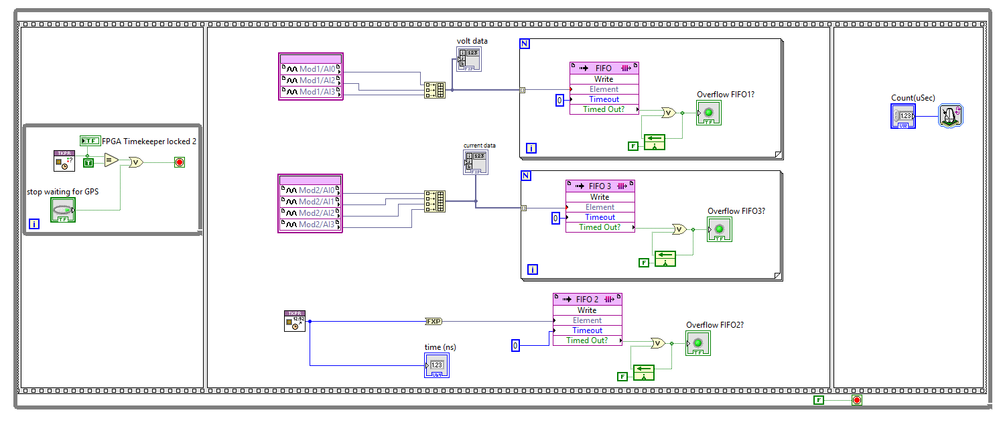

Thanks for your advice. I split the modules onto two FPGA I/O nodes and passed them to my host VI in two separate FIFOs - I now have 100 kHz on both modules. Picture of my revised FPGA code is attached for anyone with a similar issue.

Best Regards,

Eddie