- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Xilinx CIC 4.0 Kintex 7 target (2015 and 2018)

03-11-2019 04:39 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have some problems with porting some code from Virtex 5 to Kintex 7 (LV 2015).

When trying to implement a CIC filter analog to how we have it on a Virtex 5 target, it seems that the port widths / datatypes defined in the Xilinx portion of the configuration is not reflected in the LV portion of the configuration. Regardless of my settings, input is defined as 24 bit and output 32 bit with a 16 bit value for channel index.

I've tested also in LV 2018 and see the same thing there.

Is there anything about this IPCore in specific I should be aware of or do I need to implement the CIC filter myself?

03-11-2019 11:34 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

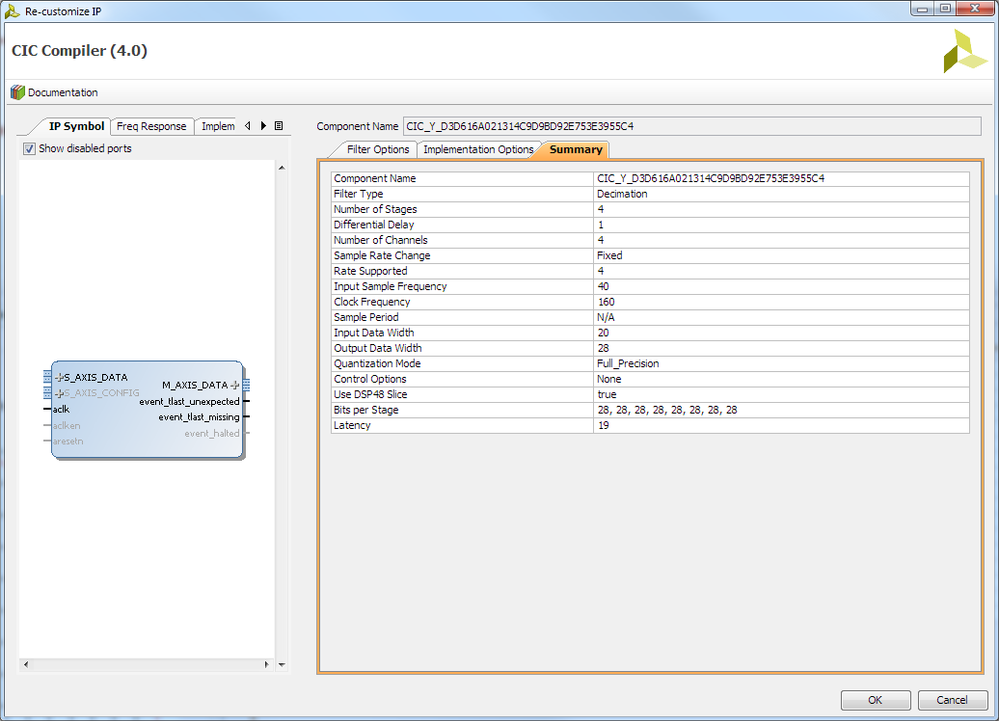

So in these two images, normally the bit widths of the data configured in the CIC Compiler 4.0 dialog (first image) and those later in the LabVIEW dialog (second image) match but here they do not.

I've converted 15 different IPCores from Virtex 5 to Kintex 7 in LabVIEW 2015 and this is the only one I've encountered so far which behaves like that.

03-11-2019 12:23 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

For clarity, in the lower image:

FXP<+,24,24> should be only 20 bits wide

FXP<+,32,32> should be 28 bits wide and

FXP<+,16,16> should be 2 bits wide.