- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

UDP Communication NI-9194 using CPU

12-12-2022 05:44 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

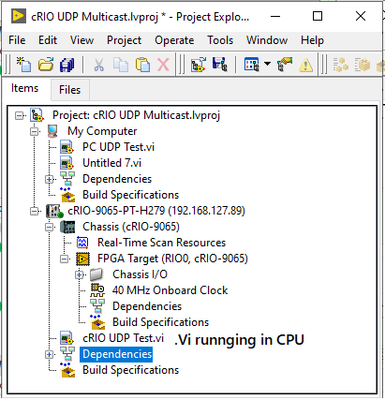

Hello, in the past i used a cRIO NI-9065 (with a Zynq SoC) with this chasis it possible to use the FPGA Target + CPU to handle the communications, like in the following example:

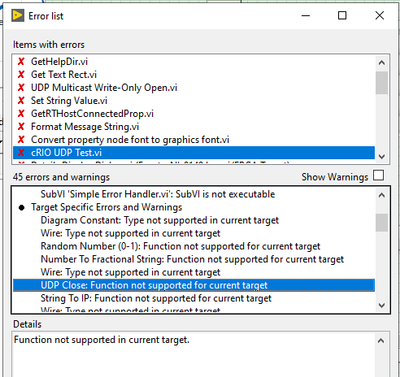

Now i need to use a NI-9149 (Ethernet RIO Target) which has the same chip than the NI-9065, but with this chassis is not possible to run the .vi in the CPU, and all the communication blocs are not supported in the FPGA Target:

Does anyone know how if it's possible to use the NI-9194 the same way than the NI-9065 with the CPU + FPGA ?

Thanks.

12-12-2022 07:26 AM - edited 12-12-2022 07:29 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

AFAIK, that's the main difference between the 90xx and 91xx chassis'. You don't have access to the realtime OS on them as it is a fixed personality without possibilities to deploy code to. And UDP functions on FPGA level are not implemented, it would be theoretically possible, to do that using the Xilinx IP blocks but considering the chip on them it is likely going to be to much for the FPGA resources.

12-12-2022 08:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you very much for your reply.

As i supposed, all clear now.

Jordi Anglada