ni.com is currently undergoing scheduled maintenance.

Some services may be unavailable at this time. Please contact us for help or try again later.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Timing errors in SCTL code

04-05-2022 09:09 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello, I'm just now learning about efficient coding in FPGA and I've run into a wall.

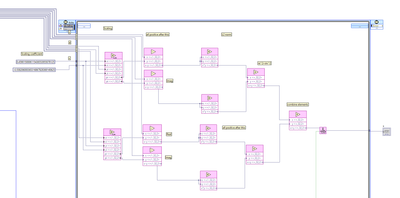

I'm trying to implement code in a SCTL where each input element (real and imaginary components) is 1) scaled by a complex coefficient c, 2) the difference is found with respect to a reference value, and 3) the squared L2 norm of the difference is computed. The input vector is split into 2 pieces and processed element-wise in parallel. To achieve the required accuracy, I need around 32 bits precision (note: all values are [-1,1] which is why I've limited the word and integer length for all operations).

My problem is that the code (attached) produces timing violations and exceeds the SCTL limit of 25 ns. I've tested for 20 bit word lengths (which is just at the accuracy limit) and still have timing errors. I know I could implement pipelining but this would delay my result at least 1 cycle which would mean that the computation of the coefficients c would start accumulating (big picture: for many different input vectors, the coefficient c is computed and fed into this code as a scaling coefficient, the output of this code is the norm(error)^2. ).

Is there any possible way for this code to be executed in one cycle without pipelining? And, if not, is it better coding practice to pipeline or to slow down the clock of the SCTL?

Thank you for any help you can provide!

04-05-2022 11:04 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi akarpilow,

@akarpilow wrote:

Is there any possible way for this code to be executed in one cycle without pipelining? And, if not, is it better coding practice to pipeline or to slow down the clock of the SCTL?

Well, the usual recommendation is to use pipelining!

Not all code will fit within the "1 clock cycle" of your SCTL, so you need to provide means to run things in parallel - by pipelining…

Do you need the SCTL at all? Can't you use a default FOR loop?