- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Sample Delta-Sigma Module and Scanned Module Synchronous

Solved!04-22-2016 01:55 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello LabView Community,

I wonder how to sample input signals of an delta-sigma module and a scanned module (SAR) at same time. I did a lot of investigation and testing during the last days but now I haven't any furhter ideas to solve my problem.

My basic test setup is as follows:

- cRio 9033 controller

- analog input module NI 9206 (SAR type)

- analog input module NI 9244 (delta-sigma type)

I have connected a 50 Hz sine signal of an external signal generator as a test signal to AI0 (+) and AI8 (-) of NI9206 and in parallel the same signal to AI0 (+) and Neutral (-) of NI9244.

I have configured AI0 of NI9206 for differential measurement and set minimum conversion time to 20 µs. The data rate for NI9206 is set to 50000 kS/s.

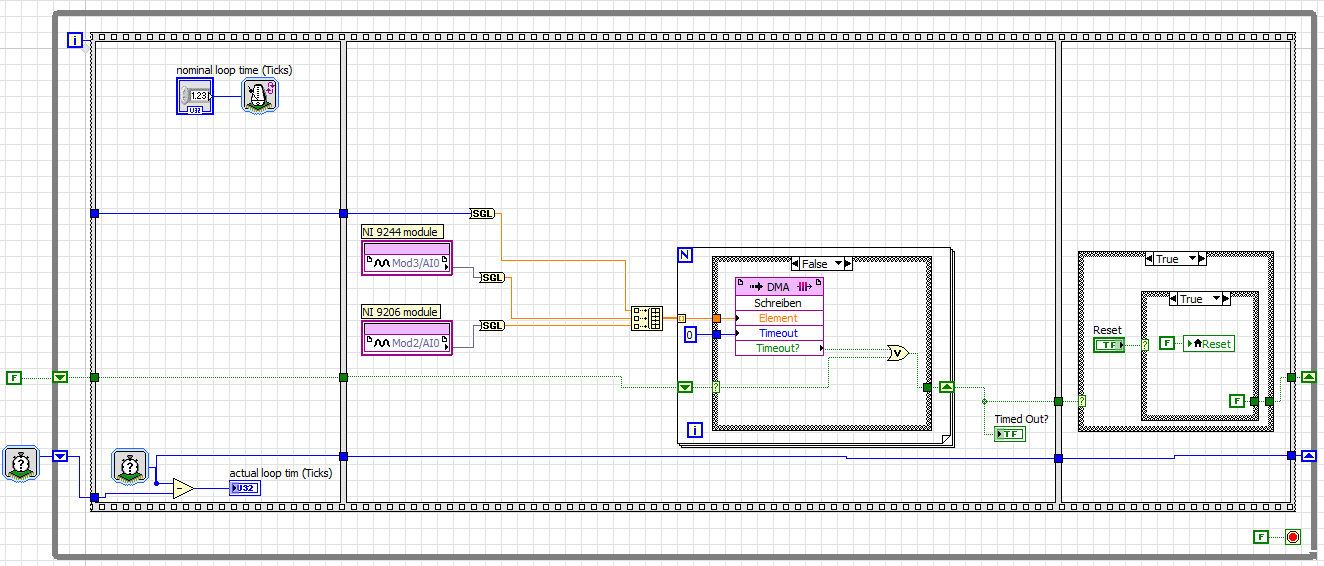

Now I like to sample data on the FPGA put it into an DMA to Host FIFO and do further processing on the cRio controller. The FPGA VI looks like this:

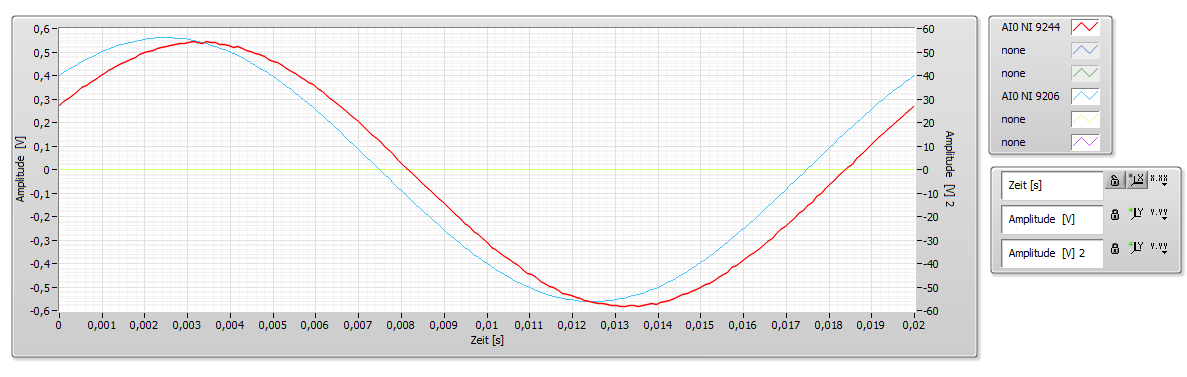

My the problem is that there is always a considerable delay between sampled signals of both modules of about 0.6 to 1 ms as you can see on the following graph:

This delay keeps constant during program execution. There is no further drift. So I wonder why this happens?

My ultimate purpose is to do power analysis like the way they do in the example "Power Quality Applications (cRio)" included in the NI Electrical Power Suite. Therefore I like to use NI 9244 to measure line voltage and NI 9206 to measure line current with the help of an additional current transducer.

Thank you a lot for a response in advance.

Best regards,

Stefan

Solved! Go to Solution.

04-22-2016 02:23 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

What you are seeing is an inherent property of using a Delta-Sigma type device. The value you can retrieve from the device is always a little stale due to the unavoidable delay in the conversion process. When you request a new conversion from your 9244, the value you get back is what the signal *used* to be a little while ago. There's a formula for this delay in the user manual on pg 37.

I know that even with DAQmx and Windows it can be tricky trying to sync data streams between "standard" DAQ cards and Delta-Sigma cards. I'm afraid I don't have the FPGA background to have any particular insight there. Just confirming that what you're seeing is indeed expected behavior.

-Kevin P

04-25-2016 01:43 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

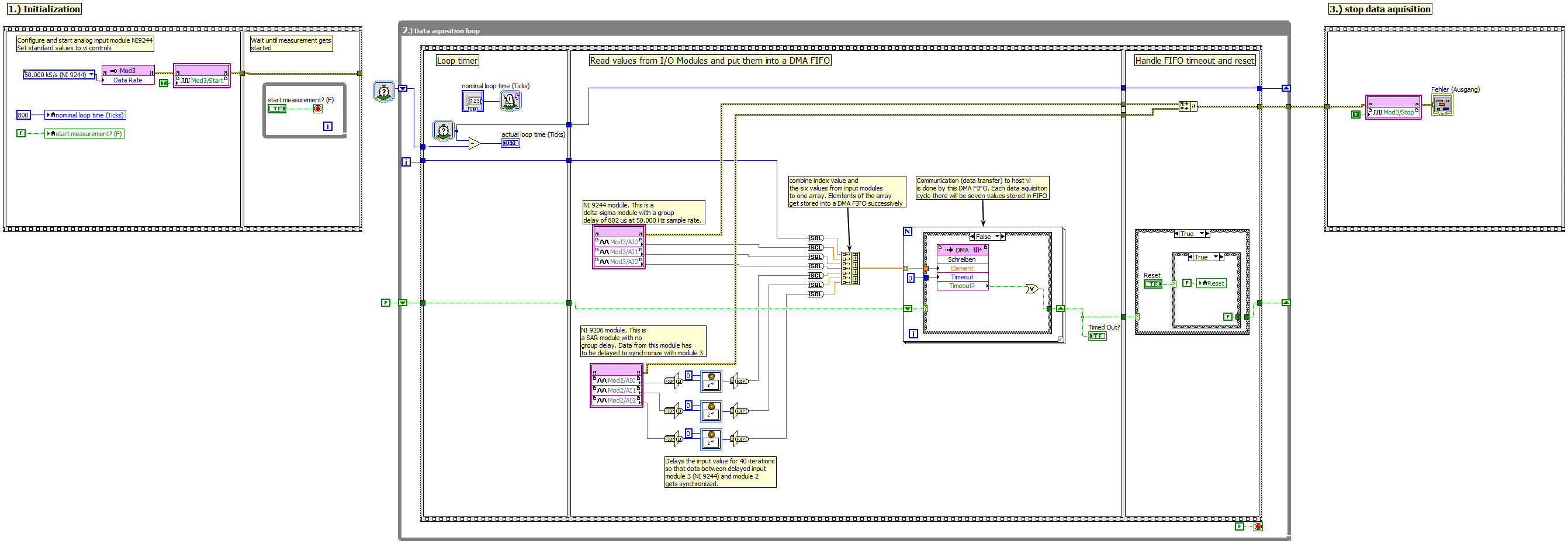

perhaps this explains what you are experiencing and by the way I added a screenshot of how to sync Delta-Sigma modules with non-Delta-Sigma modules.

How Can I Compensate for Different Group Delays with C Series Modules in LabVIEW FPGA? - National Instruments

http://digital.ni.com/public.nsf/allkb/74EB238E1BCADD528625735300681A7D

Why Is My Data Delayed When Using DSA Devices? - National Instruments

http://digital.ni.com/public.nsf/allkb/F989B25FF6CA55C386256CD20056E27D?OpenDocument

Best regards,

Christoph

National Instruments

Certified LabVIEW Developer (CLD), Certified LabVIEW Embedded Systems Developer (CLED)

Don't forget Kudos for Good Answers, and Mark a solution if your problem is solved

04-26-2016 03:24 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear Christoph and Kevin,

Thanks a lot for your great help. With your hints I was able to solve my problem. I feel a bit embarrassed haven't seen the information about input delay in the data sheet. Unfortunately it is not so easy to find this information for someone who started developing with cRio and NI delta-sigma modules for the first time. Furthermore I read a lot in the NI cRio developers guide - in particular section "Synchronizing Modules". On page 120 there is the same hint then you gave Christoph (put both I/O-Nodes in one data acquisition loop) but this is not enough to get values of the same "timestamp" from both modules. To realize that I added an extra delay to the data from the faster SAR module of 40 cycles. I have configured cycle time to 800 ticks so the delay of 40 cycle results into a time delay of 800 microseconds. That’s the input delay given in the data sheet of the delta-sigma module for a sampling rate of 50 kS/s.

Now I can measure and see two sine signals that both overlaps perfectly. In the end my FPGA vi looks like this:

This morning I found some additional information in cRio developers guide on page 115 and 116. For everyone else with similar questions I can suggest this guide.

Thanks a lot!

Best regards,

Stefan

06-17-2016 05:57 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Smurfup,

Thank you so much for this solution !

We faced the same problem (800us delay) and now we know why.

We also have different delta-sigma modules and therefore different delays.

Could you explain to us how you came to the 800us result ?

We found this kind of formulas : 40x(5/512)/Fs + 1.7us in the NI documentation.

But we could not make sense of it as the result would be close to 41,7 us and not 800...

We are really lost on this one ![]()

Thanks for any insight.

JP

---------------------------------------------------------------------------------------------------

Tout le succès d'une opération réside dans sa préparation. - Sun Tzu

06-17-2016 06:50 AM - edited 06-17-2016 06:55 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi again,

We think we found the answer.

There seems to be some incoherences in the documentations between modules...

The correct formula would be with an addition instead of a multiplication :

(40 + (5 / 512)) / FS + Xus

(be carreful to put everything to the same unit (seconds).

For a frequency of 50kHz, it would give :

40+5/512/FS = 800us (rounded)

And for each module then you should add the specific delta :

9244 : 1.7us

9234 : 3.2us

The 9225 is different as it's formula is :

38.4 / FS + 3us

And you got your delays...

Maybe I'm just being paranoid, but I think there are a lot of applications with incorrect phases out there ![]()

---------------------------------------------------------------------------------------------------

Tout le succès d'une opération réside dans sa préparation. - Sun Tzu

06-17-2016 08:08 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi JiPé,

you are absolute right about the formula. It's a bit unclear. I strumbled upon this too. Long time ago I learned in school that a fraction like 20485 / 512 or (40 + 5/512) can be written as 40 5/512 (it's also possible to type it that way into my casio calculator). But after school I never used that again because it's more common to use formulas without multiplication dots and it's no good idea to mix both forms together.

Good luck for your further software development.

Best regards

08-30-2018 03:45 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear All

In the new datasheets of C series module like NI-9235 the formula for a delay it is very precise (39 + 221/1024)/fs + 12 μs.

Use of improper fraction in the older datasheets can be misleading.

A very useful topic!

Best Regards

Przemek