- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SCTL & NI9401: Basic Questions

02-02-2014 07:53 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hy,

i got some questions about the execution time of the SCTL with I/O of the 9401 Module.

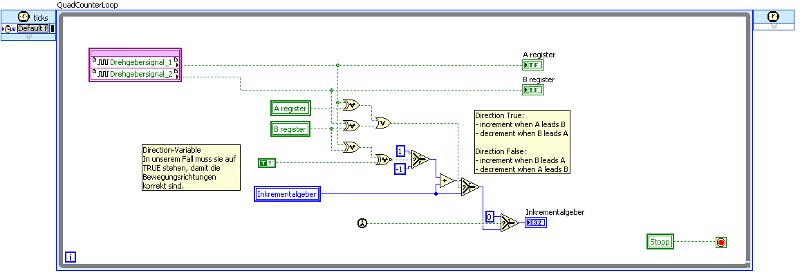

E.g.: I got an quad encoder, to read in the signals i use a sctl with a 40Mhz clock.

The sctl will execute the code inside within one tick (25ns), but now i saw in the spec. sheet that the I/O Input of the 9401 Module got an latency of 100ns.

What does that mean regarding to my sctl and the input states of my modul?

Thanks a lot.

Greetings,

Ben

02-02-2014 08:09 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

latency is just a delay. It means that it takes 4 cycles for your measurment to get to your FPGA. It will not affect your code at all. All it means is that the first 4 iterations will be using default data.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

02-02-2014 08:15 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

So it means that i get every fourth execution of the SCTL the current value of my Input?

02-02-2014 08:21 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

No. It just means that the true level you are measuring is from 100ns ago. It doesn't matter what iteration you are on.

There are only two ways to tell somebody thanks: Kudos and Marked Solutions

Unofficial Forum Rules and Guidelines

"Not that we are sufficient in ourselves to claim anything as coming from us, but our sufficiency is from God" - 2 Corinthians 3:5

02-03-2014 05:22 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Mhh...

I'm a little bit confused.

Its clear for me that the execution of the sctl will finish within one tick (25ns).

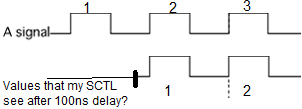

My hardware got an delay of 100ns. If my signal looks like that:

Is it right that all further signal will be acquired with an total delay of 100ns?

03-24-2014 01:36 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey,,

Yes, that's right, your incoming signal will look like this. It's link when you use pipelining in a SCTL, although you will get an output every tick, it will we corresponding to an input that happend several cycles ago.

But you should not forget considering the maximum switching frequnecy. A assume the signal you've drawn is just for explaination purposes.If you gonna have more than 2 active input channes on your NI 9401, you will be limmited to 16 MHz...