- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Reading the Pulse Count for Incremental Encoder

Solved!04-10-2024 01:57 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi rishab,

@rishab_kr wrote:

Can anyone help me to convert this VI for SbRIO 9627 ?

I mean can someone create the given VI usable fort FPGA.

Please stick with your thread…

That VI is missing a lot of subVIs and type definitions.

And it misses its project: I already explained that RT/FPGA VIs depend on information stored inside the project file!

04-10-2024 02:30 PM - edited 04-10-2024 02:31 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Think about it.

Your encoder has 4096 steps for each revolution (360 degrees) ~ 11.378 pulses per degree. It should provide about 512 pulses per 45 degrees. If it is producing less, you are under sampling (Nyquist). When you spun the encoder 45 degrees it looks like you may have gone more than 60 degrees for that change in readings. Is that possible?

If you drive between traffic lights, when the one you are at turns green while the other is red, you accelerate then decelerate. Your velocity increases from 0 then decreases to 0 at the next red light. Is that what you are seeing?

If it helped - KUDOS

If it answers the issue - SOLUTION

04-11-2024 01:56 AM - edited 04-11-2024 01:58 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi, GerdW

Yes, I understand. I will take care from next time.

Let me put my question bit clearly. As already posted about my quarry related to Incremental Encoder. I tried to count the Pulses but it not showing proper results (already mentioned). So, what I want to try is I have myRIO in which the toolkit gives an inbuilt Encoder VI which takes care of the count. Is there any way to convert that file into FPGA file and Host File if yes, I will try to find the project and share with you.

Or is there other inbuilt VI for SbRIO devices which also give the same feature?

04-11-2024 04:22 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

GerdW,

While using myRIO there is custom Encoder block is present in the myRIO. I don't know where I find the project file of this block.

04-11-2024 04:43 AM - edited 04-11-2024 04:45 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi rishab,

I don't have the myRIO toolkit/module installed (and will not).

But you can replicate the encoder function using your own VI:

- All it needs are 4 inputs (encoder ABZ signals and a ResetCount flag) and the encoder count output.

- Inside this VI you will have just boolean operations and an integer encoder count, with keeping current state in a feedback node.

- As this VI doesn't need any hardware at all you can test it even in the "My computer" target with minimal effort. Once you're satisfied from testing you can move the VI into your RT or FPGA target…

Generic recommendation:

Split your tasks into smaller sub-tasks (see above). Test your routines as much as possible BEFORE deploying to a FPGA target…

04-11-2024 05:09 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks GerdW for your constant support,

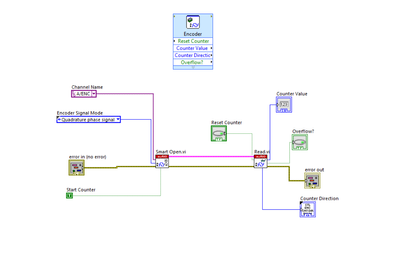

I have some quick questions, While opening it seems like this,

1. After scrolling about an hours, my question to you is this VI is myRIO Hardware dependent, will I be able to convert this VI for my requirement ?

2. what should be the best approach in your view, how I replace the myRIO files into SbRIO required file ?

Pls; I have attached the Zip as well.

04-11-2024 05:50 AM - edited 04-11-2024 05:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi rishab,

@rishab_kr wrote:

I have some quick questions, While opening it seems like this,

1. After scrolling about an hours, my question to you is this VI is myRIO Hardware dependent, will I be able to convert this VI for my requirement ?

2. what should be the best approach in your view, how I replace the myRIO files into SbRIO required file ?

In the folder "Customized FPGA\Sub VIs\Encoder" you find all you need.

Encoder.vi is the main function and completely hardware-independent!

04-11-2024 09:05 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi GerdW,

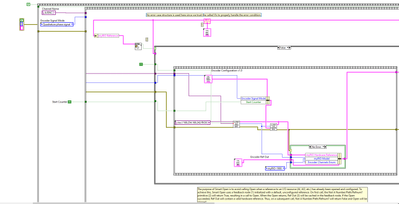

I did this and running it into the FPGA,

also, I am not getting that why when I am rotating the Motor the count is not increasing. Also what is the significance of CNFG and STAT, what shall I provide into this,

04-12-2024 02:58 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi GerdW,

I am working from many hours and could not able to figure out, about the Motor Configuration. Will it be possible for you to share some insight on it.

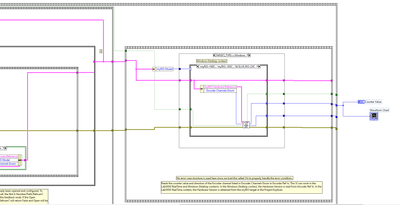

The Input to this VI is Phase A , Phase B and Configuration. They have written something about it but I am not able to understand what shall I give input as configuration.

Pls-

Right now I am trying to write a more optimized FPGA pulse counting code for SbRIO-9627 usage by taking the reference of myRIO Encoder inbuilt code. The Encoder I am using is IER3-4096 of Faulhaber.

04-12-2024 03:12 AM - edited 04-12-2024 03:20 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi rishab,

@rishab_kr wrote:

The Input to this VI is Phase A , Phase B and Configuration. They have written something about it but I am not able to understand what shall I give input as configuration.

Why don't you just drop the Encoder.vi into your own block diagram and use it as encapsulated subVI?

The configuration byte contains some bits/flags: you can analyze their meaning by following the wires in the Encoder subVIs!

You need to:

- enable (bit#0=TRUE)

- use signal mode (bit#2=FALSE)

Again:

You can test the VI behaviour using your own test data in the "My computer" context/target without compiling for and running on FPGA!