- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

RT Parallel FPGA Reference

08-03-2021 01:22 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

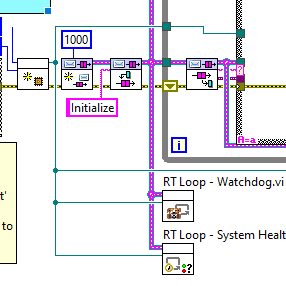

Can anyone explain to be the ramifications of having multiple parallel loops all accessing the same open FPGA reference? As an example, this technique is used in the CompactRIO Project Template.

Are there any hidden mutexs on the reference? What happens if multiple loops all try and read from the same variable?

Thanks,

Tom

08-03-2021 06:09 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The ability to access the same FPGA VI reference is benefit. Often times we access data or FIFOs from more than one loop.

The system should be designed to not try to set values from more than one loop.

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

08-04-2021 08:00 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for the reply.

So, no hidden gotchas?

08-04-2021 08:22 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Your comment reminded me what a wise friend told me once. "you always need to know the gimmies and gotchas of any technology."

Ask about more scenarios that you are concerned about being gotchas and we'll analyze them here.

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

08-04-2021 08:28 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks Terry,

I don't have any particular concerns. I have seen plenty of code that does it, but I have never found a detailed reference going into how the reference actually works under the hood. I just don't want to accidentally run into some resource contention.

Tom

08-04-2021 03:59 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

These are my FPGA VI reference links:

-

Open and Close of LabVIEW FPGA VI References

-

Opening a Reference to an FPGA VI, Build Specification, or Bitfile (FPGA Interface)

-

Open Dynamic Bitfile Reference Function

-

Multiple FPGA VI References

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

08-05-2021 07:49 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks. Primarily, reference 4 is some of the information I want.

Personally, I would like more information about the last sentence:

"The only type of access that you can always make safely using multiple FPGA VI references is reading controls and indicators."

I am looking for more information on the other not "always" cases.

Regards,

Tom

08-05-2021 08:03 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

There are NI presentations (which I cannot find) which talk about maximum number of references and other technical details.

I would check the same help article under newer versions of LabVIEW and see if there is anything new.

Which reminds me that NI has not updated online help links since 2018. We are always linking people to 2018 help. This problem has been taken up with NI here: https://forums.ni.com/t5/Feedback-on-NI-Community/User-manuals-not-updated-on-NI-site/td-p/4160150.

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications