- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Questions about the High Throughput Math Functions

Solved!03-16-2017 10:46 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

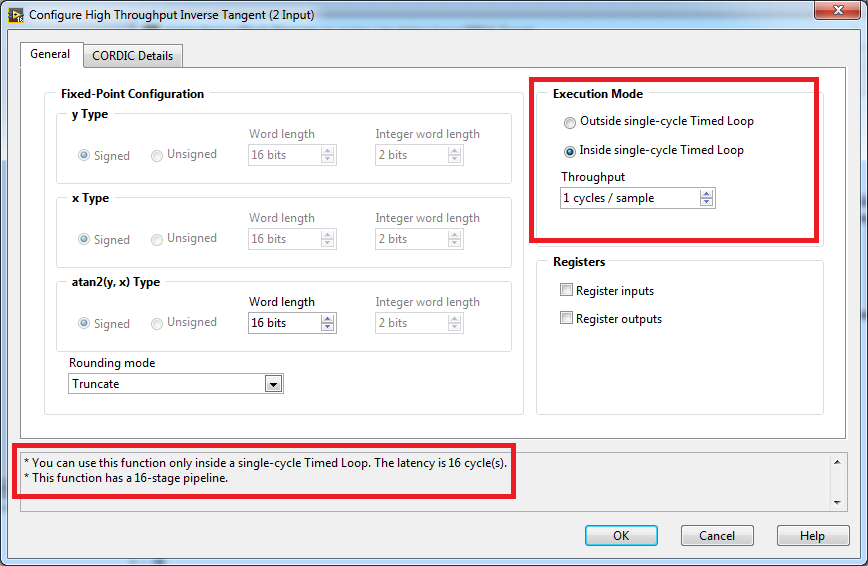

Hello everyone, now I'm working on a LabVIEW FPGA project. I'm using high throughput math function--Arctan2 which is implemented in SCTL. The X and Y are two adjacent points from AI of NI 5783, so here I used a feedback node.The block diagram is shown as follows:

Now the problem is that when the program runs, the Arctan function can only output limit points, after a while, the output value doesn't change. The input valid and ready for input keeps false. I hope I can get solutions from you.

Thank you

Solved! Go to Solution.

03-16-2017 01:42 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi! Is it possible that your "FPGA-to-Host 2" FIFO is overflowing and putting back pressure on the Arctan function? If the arctan function is receiving a FALSE for "ready for output", it should not output valid data. You can check if this is what is happening by wiring a TRUE to the input of "Ready for Output" on the Arctan function, and monitoring your Numeric indicators.

FlexRIO Product Manager

03-16-2017 03:02 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi, thanks for replying.

Yes, if I wire a true to the ready for output, the arctan can output data continually, but I think Arctan2 function might take several cycles to execute, so multicycle nodes does not return valid data every clock cycle. That is why we need handshaking. If I make the ready for output always true, it might bring some invalid data to the FiFO?

Also, I didn't put FIFO.Read successfully in the host VI. I still have questions about FIFO actually. I think the FIFO has storage limit. As the data comes into the FIFO.Write, do we have to make FIFO.Read output the data? Otherwise will the FIFO.write out of storage because of this?

Thank you

03-16-2017 03:08 PM - edited 03-16-2017 03:09 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hey! So this is actually good news. Wiring TRUE to the input "Ready for Output" was just a test to see if could narrow down the problem. It sounds like your DMA FIFO is overflowing, and when it does, it tells the Arctan function that it is not ready for new data by setting "Ready for Output" to FALSE. I believe that once you get your DMA FIFO working, you should be all set. You are correct that these nodes do not output valid data every cycle, but they indicate that to the downstream node by setting "Output Valid" to FALSE. "Ready for Output" is a way for a downstream node to tell an upstream node that it is "full" and not ready for new data.

FlexRIO Product Manager

03-16-2017 03:42 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@zyb1003 wrote:

Also, I didn't put FIFO.Read successfully in the host VI. I still have questions about FIFO actually. I think the FIFO has storage limit. As the data comes into the FIFO.Write, do we have to make FIFO.Read output the data? Otherwise will the FIFO.write out of storage because of this?

Yes, FIFOs absolutely have limited storage. There are two sides to the FIFO storage: one on the FPGA, the other on the host. You configure the amount of storage on the FPGA when you set up the DMA FIFO. You can (but do not need to) configure the size of storage on the host through a method node. The host-side storage should usually be much larger than on the FPGA. Data is automatically copied from the FPGA storage to the host when the FPGA storage fills, for a target-to-host FIFO. If you don't start the DMA channel from the host, then the FIFO will fill when it reaches the amount of storage allocated on the FPGA for that FIFO.

03-16-2017 04:27 PM - edited 03-16-2017 04:30 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@zyb1003 wrote:

but I think Arctan2 function might take several cycles to execute, so multicycle nodes does not return valid data every clock cycle.

The high throughput arctan function can return a sample every cycle. However doing so inserts several cycles of latency. If the latency isn't an issue, you can give it a new sample every cycle.

03-16-2017 04:45 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi, thanks for replying!

I try to add FIFO.Read to the host VI. But it seems to be some problem with that.

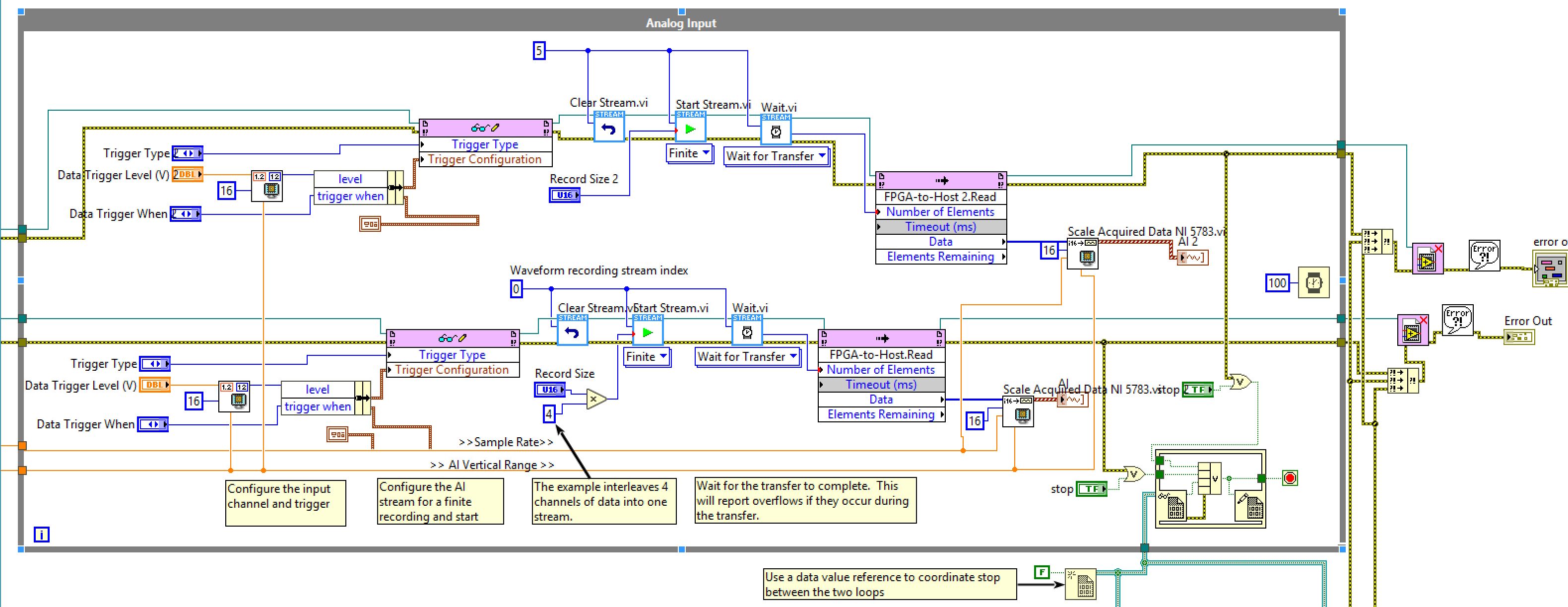

My project is based on NI 5783 example. As you see in the previous picture, I created a FPGA-to-Host 2 Write in my FPGA VI. Then I add FPGA-to-Host 2 Read in the host VI as following pictures. The reason I want to use FIFO is because I want to make the Arctan (X/Y) to be my phase input of the AO in the host VI.

I wire the FPGA-to-Host 2 the same way as FPGA-to-Host in the example. When the program runs, it shows error at the input of clear stream.vi. For convenience, I also attached my project file.

Please see if there is anything you can help me with this.

Thank you!

03-16-2017 04:55 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you so much for replying me!

Now I have deeper understanding of FIFO. As you can see at the above reply, now I have some trouble with wiring the FIFO read function. Please check this to see if you can help me with that.

Thank you!

03-16-2017 04:58 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Oh I didn't notice that. That's good for me. Thank you so much. And I also have problems with wiring the FIFO read in host VI. Please check the above reply to see if you can help me with that.

Thank you!

03-16-2017 04:59 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Don't split your FPGA reference wire, and definitely don't try to close the FPGA reference twice. Configure the DMA FIFOs in sequence. Inside the loop, why are you writing two different values to the same controls on the FPGA (for the trigger)? There's only a single stream control in the FPGA VI, so why are you trying to configure it twice on the host?

At the end, what specific error are you getting, rather than saying you get an error?

You might consider packaging both data items together into a single FIFO, rather than using two FIFOs. Since you appear to be using 16-bit values, make the FIFO hold a 32-bit value, then put one number in the upper 16 bits and the other in the low 16 bit (or, if you need more bits, make it a 64-bit FIFO and then you can store two separate 32-bit values in it).