- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Programmatically initialize FPGA Read Only Memory

02-07-2022 02:10 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have a VI that interfaces with an FPGA using the following process:

1) Vi opens a configuration file and reads an equation Fx(X,Y)=Z.

2) The Vi runs the equation and creates a block of memory (Mz) of Z from (0,0) to (300,300).

3) The Vi uploads Mz to the FPGA

4) The FPGA takes signal inputs, runs them through Mz, and returns modified data.

Currently, I have a working system for this process. However, for step 3 I use a FIFO to construct Mz on the FPGA. However, this uses a Host to target FIFO slot that would be otherwise available.

Is there a way to configure the memory inside the FPGA at initialization without using a FIFO in this way?

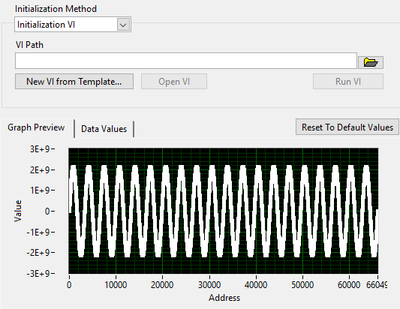

I know this menu works in the project to set initial values before compilation, but is there a programmatic way to do this after the FPGA and VI are complied?

Considerations:

- The VI will be compiled into an exe.

- The configuration file will change every 3 months.

02-07-2022 02:20 PM - edited 02-07-2022 02:21 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi JS,

@JScherer wrote:

Is there a way to configure the memory inside the FPGA at initialization without using a FIFO in this way?

To send data from host to FPGA you can use:

- FIFOs

- controls on FPGA main VI frontpanel

When you don't want to use FIFOs you should use controls: implement a handshaking algorithm using a control for your data and one or more boolean controls for handshaking between host and FPGA…

(It will take some iterations to send your 90601 elements using this way.)

02-07-2022 02:47 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@GerdW wrote:

implement a handshaking algorithm using a control for your data and one or more boolean controls for handshaking between host and FPGA…

(It will take some iterations to send your 90601 elements using this way.)

Understood, I was afraid I'd have to build that system of controls/latches to write and check 90k elements. I think that's likely not worth the time considering the efficiency loss.