- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Passing data from RT host to FPGA through DMA FIFO

Solved!02-03-2012 06:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

I am trying to write some data from an RT host to FPGA target using DMA FIFO then process this data and then read them back from the FPGA target to the RT host through another DMA FIFO. I am working on NI PXIe chassis 1062Q, with NI PXIe-8130 embedded RT controller and NI PXIe-7965R FPGA target.

The problem I am facing is that I want to send three different arrays, two of the same size and the third one with different size, and I need the smaller one to be sent to the FPGA first. I tried using flat sequece with two frames in the FPGA VI. In the first frame I read and write the first array in a while loop which is finite (i.e., finite number of iterations). The second frame contains the process of reading and writing the second two arrays (of the same size) in a while loop that can be finite or infinite (according to a control). The problem is that this didn't work. The 2 arrays are displayed on the front panel of the RT host VI and are working fine, however, the array that should have been read in the first sequence doesn't show up on the front panel of the RT host VI. This doesn't make sense because if it is not passed from the host to the fpga and vice versa then the second frame shouldn't have been executed. Note that I am wiring (-1) to the timeout to block the while loop iterations till the passing of each element is complete. Thus the first while loop has 3 iterations only. Could someone help me undersdtand why this happens and how to solve this problem?

I am attaching a picture of both the host and the fpga vi.

Thank you.

Solved! Go to Solution.

02-03-2012 07:27 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I would guess that your problem is abuse of local variables. You write to three different local variables of the Temp Data Array, plus the indicator itself, and at the same time you read from local variables of the same indicator. You have no idea in what order those operations occur nor what the end result will be. You need to eliminate ALL the local variables. Chain the array operations together so that the output from one goes into the input to the next, and eventually into the FIFO Write. You can use the indicator to see the value before feeding it to the FPGA. In the for loop, the local variables are easily replaced with a shift register. Once you've done all this you can also eliminate the sequence structure. Instead, chain all the FPGA operations together in sequence (the reference out from one goes to the reference in for the next, same for the error wires). This is sufficient to guarantee execution order.

02-03-2012 08:12 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Actually I have traced the RT host vi and found out that the sequence of the local variable is going as I want and I guess the problem isn't related to this part because the data is written into the local variables/indicators correctly. The problem is within the FIFO part.

However, I'd love to know how to reduce the number of local variables knowing that the operation I want to do is as follows: I initialize the "Temp dara array" with zeros then put three different elements in this array one after the other. For the "Real and Imag A arrays" I want to initialize them as well and then put the real and imaginary parts of the elements of matrix A. For example I use the "index array" block to update the elements in the array which needs the "array as a whole" as an input and once again as an output. That's why I need the local variables. I'd be glad to hear your suggestions and also if you knew a solution to the FIFO part.

Thank you.

02-04-2012 02:14 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

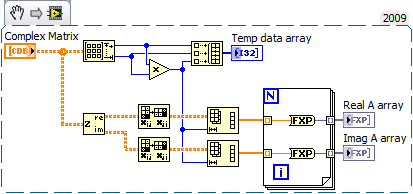

No need to initalize the arrays with values that you will immediately overwrite. Here's what I believe to be equivalent code:

The array outputs should be wired directly to the FPGA FIFO writes. Do not use local variables when you can wire directly.

If you know that you want to transfer the Temp Data Array first, why not make your code do that? Eliminate the sequence structure, and put the functions in the order in which you want them to execute. Use the FPGA reference and error wires to enforce that order. You might consider writing the Temp Data Array, reading it back, then writing the Real and Imag A arrays, to see if that gets you the results you expect. Run the code in simulation (in the project, right-click on the FPGA target and execute on the host with simulated IO) so that you can use execution highlighting and probes to see what is happening. Wire the error wires through and see if you get an error anywhere. Make sure you're not missing something simple like looking at the wrong starting array index.

02-06-2012 12:49 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks a lot..I'll try that

02-06-2012 07:29 PM - edited 02-06-2012 07:42 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

If you vote for my idea here and it gets implemented, you could even omit the FOR loop entirely. 😄

(I would also move the RE/IM split inside the FOR loop and do the transpose and reshape operations on the complex array before the loop. This way you only need one instance of these operations. You might even save some unecessary array allocations this way)

02-07-2012 07:54 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I guess this idea would work, except for removing the for loop entirely as the FXP converter needs it input to be "element" not an array or matrix.

Thanks for your help.