- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Module Synchronizing NI 9220 and 9403

11-11-2018 07:23 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi everyone,

We've been studying an implementation of data acquisition in LabVIEW FPGA, but doubts have arisen when trying to implement some code in FPGA.

Although I've searched for a while in the forums and some articles I am still curious if it will work.

In the case, we have four Modules (2 x NI 9220 and 2 x NI 9403).

The goal is to acquire these data simultaneously from the four modules, but the question is?

If we put the I/O Nodes in the same Node, can we guarantee that the data being pulled out at same time? Considering we are using standard mechanisms for controlling loop rate.

By the way, when reading the examples about the NI 9220 I saw a structure called FPGA I/O Method which differs from the standard I/O Node, but the documentation on it is very sparse. This method does not allow to read data from the NI 9403, only from NI 9220.

Regards.

- Tags:

- fpga

11-13-2018 07:53 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Felipe,

Answering your question: Yes!

According to this article, what you need to synchronize different modules is:

- The modules must use the same master timebase source

- The modules must start acquisition mode at the same time

- A single FPGA I/O Node function must read the synchronous data

In your specific case, as you your NI 9220 has a successive approximation register (SAR) ADC and the 9403 is a DI module, you just need to put them in the same FPGA I/O Node. When using Modules with Delta Sigma ADC, things get trickier, as explained in the same article I mentioned above.

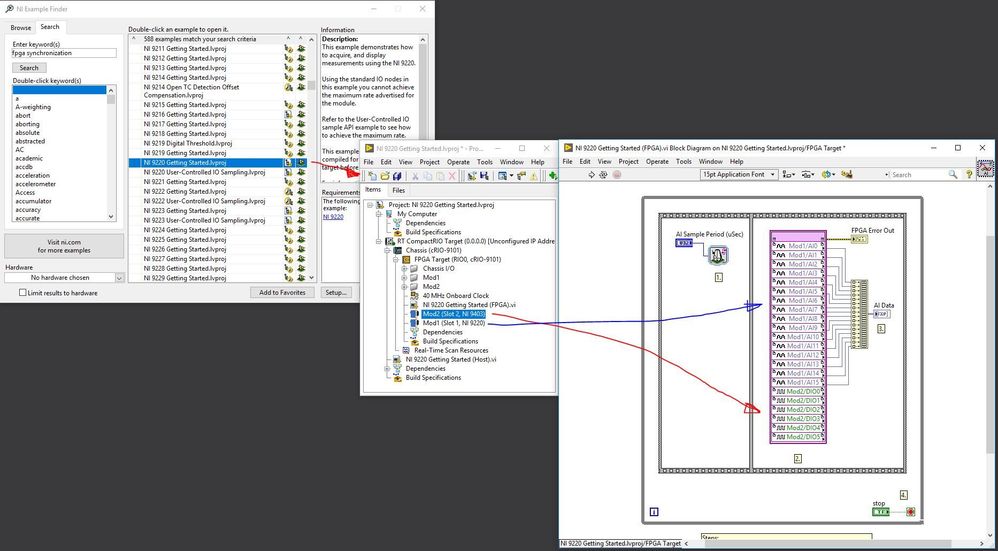

I opened an Example for the NI 9220 and added the NI 9403 to my FPGA Target. I was able to put them in the same FPGA I/O node.

Try using this project as a starting point and then adapt the code to your needs.

Hope that helps!

Best,

Technical Support Engineer

National Instruments

11-16-2018 11:55 AM - edited 11-16-2018 11:56 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thanks for your answer Felipe.

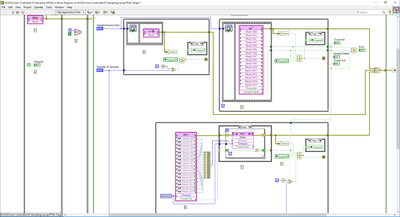

Extending the doubt, I was referring actually to the example "NI 9220 User-Controlled IO Sampling.lvproj" and the "Read I/O Method" used in the mentioned example (Picture).

Our application has to acquire 15.360 S/s, for this I think we can use a derived clock with the "Generate I/O Sample Pulse" function.

My first thought was using a standard "I/O Node", but I am not sure if it works with the "Generate I/O Sample Pulse" or vice-versa.

For solving this I think we could use in parallel an "Occurrence" function for the Digital Module, but I must be sure that I don't have any other more sophisticated solution before I go to this approach.