- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LabVIEW FPGA DIO I/O

12-19-2023 05:01 AM - edited 12-19-2023 05:04 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello!

I'm working on a signal processing algorithm in LabVIEW FPGA for a PXIE-5774 target. Everything else seems to be working fine, but I'm having trouble getting status information from my device through the DIO connector in the FPGA/digitizer.

I'm trying to read a TTL 3.3V signal as high from a signal generator through the front panel, using the right pins as shown in this link.

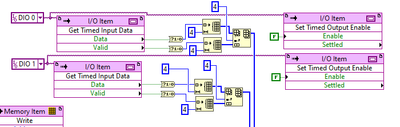

In the FPGA VI, I've set up a single-cycle timed loop with two FPGA IO method nodes like this:

Based on this documentation, I've set "Set Timed Output Enable" to False on both I/O items, and I'm trying to retrieve information from the DIO0 and DIO1 channels.

In the image above, I've transformed the boolean to an integer and formed an array that I'm sending to a channel in my stream. I can receive other integers sent to my FPGA with this method, but the problem is that "Get Timed Input Data" is not returning a 1 when it should.

Also, when I run the script, the streamed information shows everything else as 0, but the elements corresponding to "DIO0 data valid" are not showing as 1, even though they should. (So DIO1 data valid is showing false as well even though it is configured the same as DIO0)

Any insights into why "Get Timed Input Data" is not giving me the expected result would be greatly appreciated!

Aarni