- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LabVIEW FPGA 2019 Compilation error: A time error ocurred.

10-25-2021 02:43 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Guys!!!.

I am brand new on this forum, I've been working with the NI-sbRIO-9637 few weeks ago. The documentation is hidden among forums, the example does not provide full capabilities of the FPGAs, but I found a very nice trainning on internet: NI LabVIEW FPGA Part 1 - YouTube there are 117 episodes not too deep explained but they are good to start with.

So, my problem so far is that after 1 hour and 26 minutes of building process the Compilator displays A timming error ocurred. Since I am not writing the VDHL, for me it is not very intuitive how to solve the issue. Nevertheless I did my research before heading here. The error is because I am asking the FPGA to do more in a single cycle loop than it is capable of.

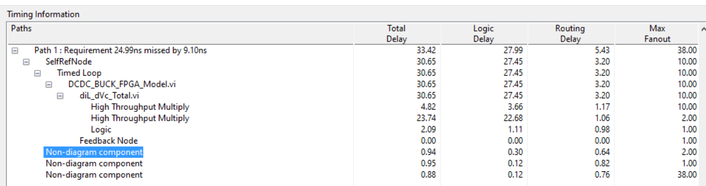

Therefore, I checked the Timing Information. It appears the error is because the entire peace of process should run within 1/40Mhz = 25ns, but the required time is missed by 9.10ns.

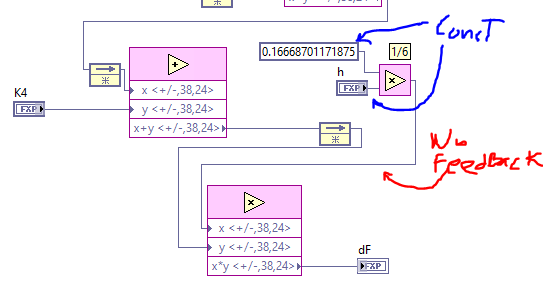

Thus, I follow the VI path listed, and I found that I had a block without a feedback node. But I though it was not necessary because the information is already available for the multiply operation, since h and 0.1668701171875 are constants.

Then I went back to the literature available for the compaq rio:https://www.ni.com/pdf/products/us/fullcriodevguide.pdf , and this non-official link: https://docplayer.net/42464504-Ni-labview-for-compactrio-developer-s-guide.html

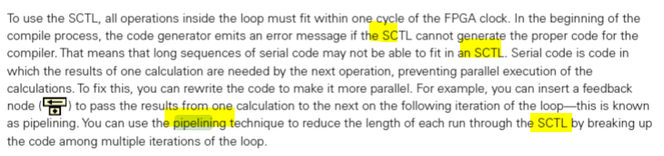

And it seems the direct connection implies a successive or series logic, so all the VI block within a SCTL should have a feeback connection in between to create the pipelining.

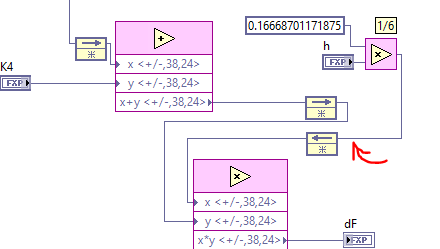

I already made the feedback connection.

Now I am going to start the compilation again.

Let's see what happens.

10-25-2021

04:54 PM

- last edited on

05-08-2024

01:39 PM

by

![]() Content Cleaner

Content Cleaner

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Feedback nodes should help with timing. The high throughput math functions have a wizard and you can turn on internal pipelining.

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications

10-27-2021 02:23 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi thank you for your answer.

I saw that but I don't understand the interface. For example division are 18 cycles/sample when I turn the SCTL mode, when I reduced the number I saw a note that describes the number of stages in the pipeline. I don't understand this and I didn't find a example or explanation yet.

Would you please send me an example of this Hight throughput math block by using pipeline wizard. Please try to do 2 or three math stages Like I am doing to make sure I am understanding this option.

Thank you in advanced.

10-27-2021

09:38 AM

- last edited on

05-08-2024

01:41 PM

by

![]() Content Cleaner

Content Cleaner

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

For reference on the SCTL see https://knowledge.ni.com/KnowledgeArticleDetails?id=kA00Z000000P8sWSAS&l=en-US

For the high throughput divide function see https://www.ni.com/docs/en-US/bundle/lvfpga-api-ref/page/vi-lib/rvi/fxpmathlib/fxpdiv/xnode/nifxpmat...

When going into an SCTL the forced time constraint has a particular impact on more (digitally) complex functions such as divide. By default it takes 18 cycles to generate a result but we can set the throughput to say 1 cycle per sample. This is done by internally pipelining the divide function. More memory/registers are used to accomplish this. Note that latency does not go down and it still takes a sample 18 cycles (depending on settings) to go through the divide function. Pipelining is an important concept for higher performance FPGA designs.

Certified LabVIEW Architect, Certified Professional Instructor

ALE Consultants

Introduction to LabVIEW FPGA for RF, Radar, and Electronic Warfare Applications