- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How Do I Programmatically Configure My NI 9469 in LabVIEW FPGA?

Solved!09-06-2013 03:15 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear experts,

Does anyone knows how do I programmatically configure my NI 9469 in LabVIEW FPGA?

I want to dynamic assign which cRIO is master and which are slaves?

In a normal way, you need to righ-click on the module in project and choose properties, then config each target as master/slave and complie them individually.

Thanks,

Justin

WPC Systems Ltd.

Taiwan

Solved! Go to Solution.

09-06-2013 03:32 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

have you looked at the Invode Methods for the module? I don't know exactly how to do this, but maybe it helps.

Tyler

09-06-2013 04:24 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Dear Tyler,

Thank you so much for reply incredible soon!

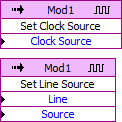

I'd tried that both property node & invoke node in labview fpga.

but still can't find the option for config master/slave

Here is the screen shot of the options:

Let me simply giving an explanation:

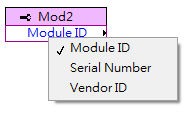

When you right-click on the module (in project) you can define it as master/slave directly and easily.

The only disadvantage is that you must compile at least two times. (one is for master, another is for slaves)

Even you have a practical design which can combine both master/slave in single FPGA VI.

You still need to compile it twice (on different target, one is master another is slave)

That's why I'm calling for help here.

Best,

Justin

WPC Systems Ltd.

09-06-2013 04:57 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

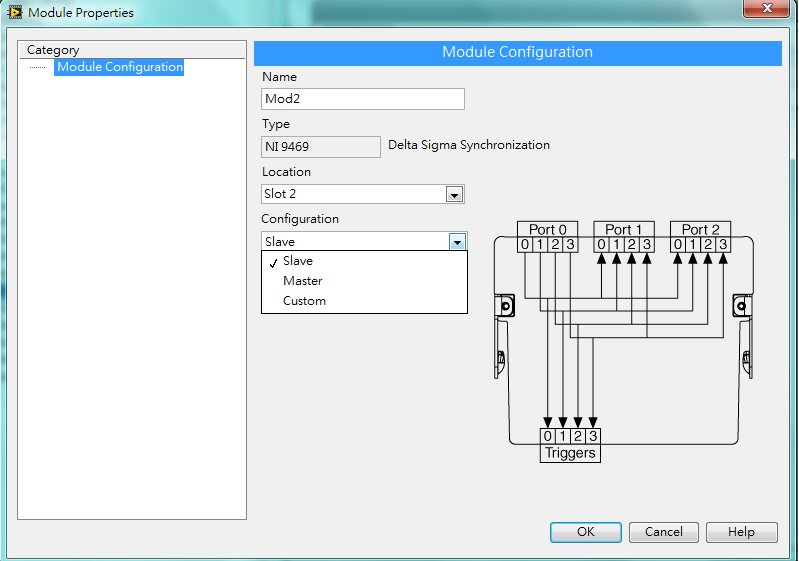

I fully understand your approach. It would be a pain to compile 2 seperate bitfiles for the desired behaviour. I've taken a look at the specification of the module as well as on the NI Example Finder. If I understood it correctly the only approach is to set the module to Custom. Then you could implement a boolean front panel element on your FPGA VI that indicates if this system should be a master or a slave. This information could be passed for example from a configuration file on your cRIO via the RT-system to your FPGA. According to this flag, set the "routing table" of your module with the invoke nodes. This is from my knowledge the only way to go to have one single bitfile for your FPGA.

Thanks

Tyler

09-06-2013 10:18 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Justin,

The Master and Slave is a predefined configuration set at the config subpanel, saying that there is no LabVIEW FPGA node that allows you to switch between those, however you can use the method nodes to reconfigure all the Ports of the 9469. If you look at the Custom Configuration Advanced subpanel, you can go back and forth between Master and Slave, and you could create a configuration array and pass it to the Set Line Source method and Set Clock Source. There is catch with this method, If the source of the Trig3 is set as any other line in any other port, it cannot be changed to have the Clock as its Source and vice versa. I really recommend you to enable the error terminals on the configuration method since they error out with useful information when you try to apply an illegal configuration.

If you want to go back and forth between Master and Slave I recommend you to set the master configuration from the config subpanel and use the previous method to go to slave configuration, and if you want to go back to the Master configuration use the restore Configuration method

Master Config Slave Config

09-06-2013 07:32 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Jullen,

Thank for your great help!

That seems a really good way to solve this problem.

I will give a try ASAP.

If it works well, I will tell you guys.

Best regards,

Justin

WPC Systems Ltd.

Taiwan

11-28-2014 06:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

Where can I find help on these methods?

I Dotnet Developer

Thank you

Mickaël