- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Frequency Measurement in FPGA

02-20-2020 01:11 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

for my application need to acquire a Square wave whit a myRIO 1900, and measure the frequency of it.

The frequency of my signal is around 20kHz,but the frequency can vary by about 10 Khz depending on the crystal conditions.

To read the frequency I made a counter in fpga, see fig1., From which I get the period of the signal which I then convert to frequency (1 / P) in vi real time.

02-22-2020 11:24 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Why do you multiply by 1M?

It seems like with a 80MHz clock, your count is number of 1/80M seconds in a full period.

As a result, to get Hz you need to take the reciprocal (as you do) then multiply by 80M, not 1M. Even if you want the result in kHz, you have the wrong multiplier (then you'd want 80k).

Otherwise, the precision of your measurement is determined by your SCTL click rate, which is already high enough to give good resolution at the frequencies you describe.

You might consider some averaging if your values are varying too quickly.

02-23-2020 02:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi,

you are right about the moltiplication by 1M, but is simply a mistake, I attached an old version.

Anyway, whit 80 Mhz of clock I' m able to appreciate the Hz variation till 4K, above this frequency the precision around the Hz begins to decrise.

Furthermore, just yesterday I have known that the frequency range has been moved from 3Khz to 100Khz, so now I have the same needs (1 HZ sensibility) but in a bigger frequency range.

I know that is it possible to use two counters to increase the sensibility in a frequency measurements, but I don't know how to implement it in FPGA.

Can you halp me?

regards

David

02-23-2020 03:01 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I'll take a look at your code when I return to a PC, but in case you haven't read it, you might find the following link helpful: Making Accurate Frequency Measurements

02-24-2020 04:06 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi and thanks for the link.

I would like to use the 2 Method(Count Number of Pulses in Known Time), I think should be the best solution for my pourpose,but I don't know how to implemet it in FPGA do you have any idea?

Regards

David

02-24-2020 09:41 AM - edited 02-24-2020 09:49 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

- Choose a measurement time

- Convert this time to number of ticks of the FPGA clock. Set this value as the input to a shift register.

- In a separate shift register, set the initial value to 0. This is basically your current setup.

- Every iteration, decrement (decrease by 1) the first shift register. If the rising edge occurs (use the code you already have) then increment the second counter (you can use the same Case Structure setup you have now, but change the behaviour). If no rising edge, just pass through.

- When the first counter is equal to 0, reset it to the starting value (use a constant or control etc) and output the value of the second counter (number of rising edges in known time).

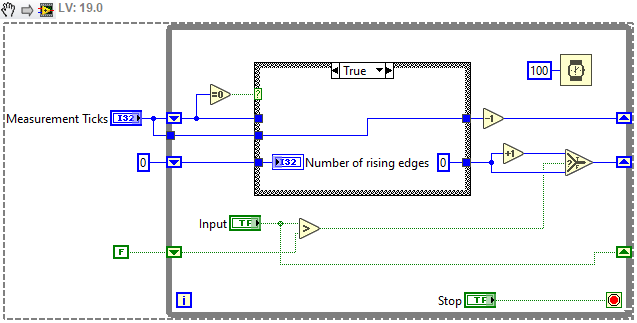

Here's a simple example showing the logic on Desktop (so with a Wait, no SCTL, boolean control as input). There is limited debugging but you could add more indicators to display updating values if it isn't clear.

02-25-2020 07:42 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

with two more shift registers you should get an even better reading 😉 and since the first edge is the last previous you could even extent the gatetime (10s? ) to get a fast and a higher resolution freq. counter

the false cases just pipe the values

Henrik

LV since v3.1

“ground” is a convenient fantasy

'˙˙˙˙uıɐƃɐ lɐıp puɐ °06 ǝuoɥd ɹnoʎ uɹnʇ ǝsɐǝld 'ʎɹɐuıƃɐɯı sı pǝlɐıp ǝʌɐɥ noʎ ɹǝqɯnu ǝɥʇ'

02-25-2020 08:29 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

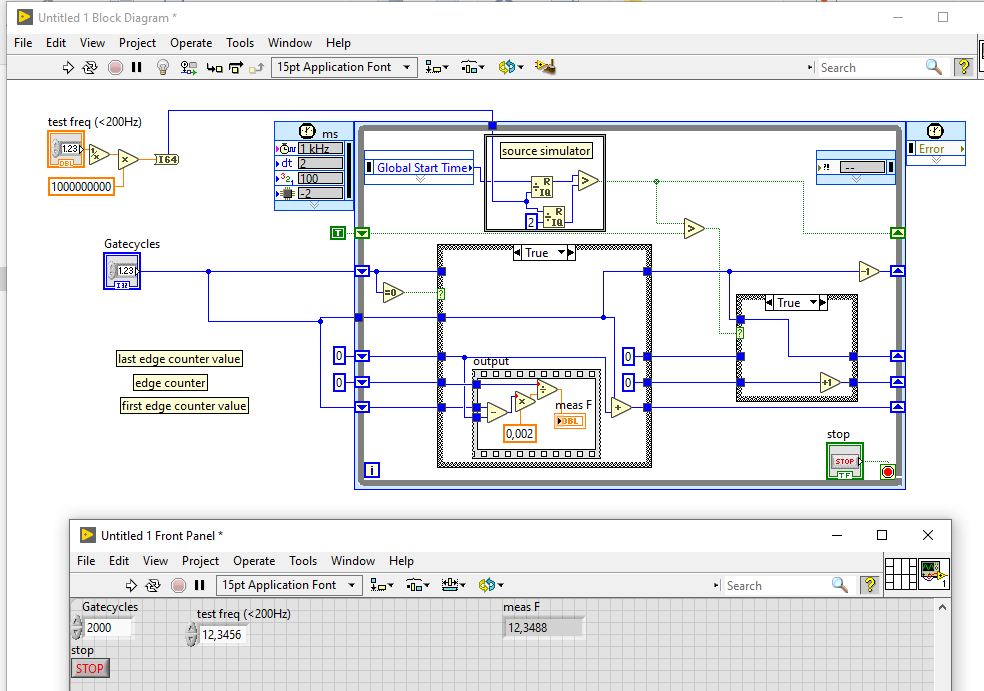

Thanks for your input,I have done a new VI (See Fig 1 and Fig 2)strating from your sketch,but some things are not clear to me :

1) when yo said"choose a meseurment time" means choose a FPGA onboard clock?

2) What is teh input of first register(Measurement Ticks)?

3) Apparently if I choose 80Mhz as onboard clock, and 80Mhz as Masurement Ticks the "Number of edge " is dierctly the frequency is it correct?

Do you have some Advice to improve the VI?

thanks

David15

02-25-2020 09:25 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Henrik,

Your solution is bit more complex for me, can you explaln it better ?

I tried to develop your VI but maybe I mada some mistake because it didn't work properly.

Please find attached the VI can you check it?

Regards

David

02-25-2020 10:07 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@David15 wrote:

Thanks for your input,I have done a new VI (See Fig 1 and Fig 2)strating from your sketch,but some things are not clear to me :

1) when yo said"choose a meseurment time" means choose a FPGA onboard clock?

By a measurement time, I meant a period of time (in seconds, for example) over which you want to make the measurement. This is a free choice, but has the following tradeoff: the longer the time, the more accurate (advantage) but the less frequent (disadvantage) - because you will get one result per measurement time.

@David15 wrote:

2) What is teh input of first register(Measurement Ticks)?

Measurement Ticks is the number of ticks that correspond to the measurement time. So if you have an 80MHz clock, and want measurements every 0.1s, then you'll have measurements at 10Hz rate and your "Measurement Ticks" value would be set to 80MHz * 0.1s = 8M.

@David15 wrote:

3) Apparently if I choose 80Mhz as onboard clock, and 80Mhz as Masurement Ticks the "Number of edge " is dierctly the frequency is it correct?

Yes - this is true. If you choose the same number of ticks as your clock rate, you'll get one measurement value per second. As a result, the number of edges per result will be the same as the number of edges/second, or frequency.

@David15 wrote:

Do you have some Advice to improve the VI?

I guess you mean the input being 100320Hz and the result being 100322 Hz? I think this almost lies within your error:

Fk = 80MHz, Fx = 100320Hz, error = Fx+-1Hz (since you're measuring for 1 second, the difference between adjacent counts is 1Hz). If you increased Measurement Ticks, you'd see this decrease, but you'll take longer to make a single measurement.

You can also try some variations (which perhaps include Henrik's post, I'm still working it out) to reduce the error further without reducing measurement frequency (for example, by checking the number of 80MHz edges in a known number of the slower ticks, rather than only using the total number of slower ticks in a specified number of faster ticks). It's not clear to me if this is method 3 in the link I gave previously - that description is actually a little unclear to me in general...

@David15 wrote:

thanks

David15

You're very welcome. Feel free to give kudos to helpful posts 😉