- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Fpga debug using simulated IO via custom VI - error message

Solved!10-16-2013 05:12 PM - edited 10-16-2013 05:20 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

I have an PXIe-7966R with MXI interface to Win7-64/LV2013-32bit. The setup is working. VI's can execute on FPGA target.

I want to debug an FPGA vi on the host computer using simulated IO via custom VI. I try to follow the tutorial in LabVIEW Help: Tutorial: Creating Test Benches (FPGA Module). Have made the custom test vi and the "inverter.vi", and set the proper simulated execution mode.

When running the "inverter.vi" (FPGA target but for now simulate on host) I get this error message dialog:

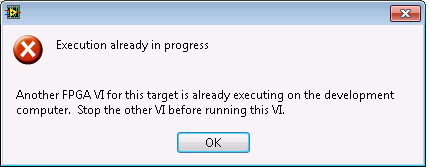

Execution already in progress

Another FPGA VI for this target is already executing on the development computer. Stop the other VI before running this vi.

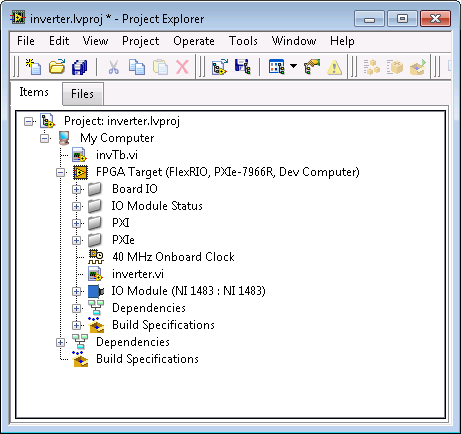

I can't see where I could stop this other fpga vi. In fact I can't find this other vi at all. Here is the project, which can't be any simpler:

Any hints are welcome.

Solved! Go to Solution.

10-16-2013 05:59 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Can you show us what the host vi looks like? Are you opening multiple references to the same FPGA vi?

Are you closing the refecence when you end the vi?

Can you try closing down labview completely, then open a flexrio example from the example finder and try to execute on dev computer?

FlexRIO & R-Series Product Support Engineer

10-16-2013 06:23 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

thanks for your quick reply.

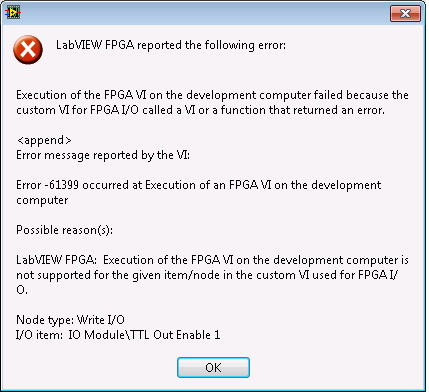

I tried restart LV and sure enough this changed things. Now I get this error

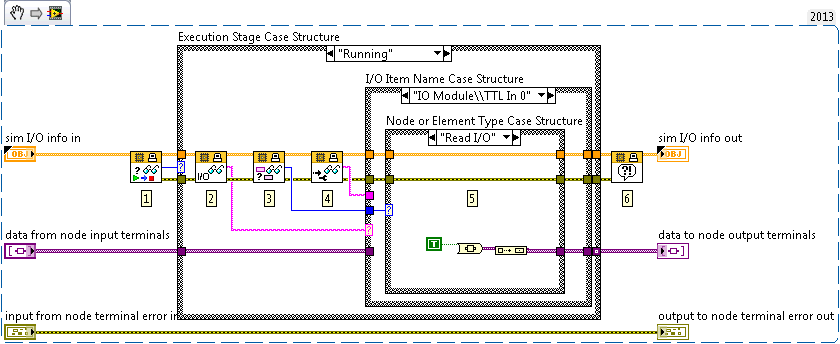

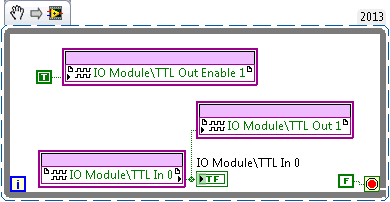

which could make sense as the IO simulation VI (simTb.vi in my project) is not tested (can't do that without the fpga target under test). This is shown in part below. Note that it is the auto generated template from fpga simulation setup dialog.

and here is the fancy fpga target vi under test (yes i try to make life easy:-))

So no host vi for communication with fpga - just the simualtion test bench.

Ok, I will work on from here and try to fix the error reported. Although I dont se any reason why it reports that its not supported to write to "IO Module\TTL Out Enable 1"

But clearly a restart made a diffence.

10-16-2013 06:32 PM - edited 10-16-2013 06:33 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

as for your other question of flexrio examples:

I have sucessfully run the example "10 tap 8 bit camera with DRAM" example project in simulation mode with random inputs.No problems reported there.

10-17-2013 06:27 AM - edited 10-17-2013 06:28 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

The error message (-61399 above) is telling that the "IO Module\TTL Out Enable1" is not handled in the Simulated IO test bench.

It is important that all IO's are dealt with in the "Simulated IO test bench". This make sense at least for FPGA inputs which need to be driven to some state.

For FPGA outputs it is not obvious why a handler for the port is required in the test bench. Any comments on that?

11-05-2013 01:33 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You are correct in thinking that simulated outputs shouldn't need a handler for the port, however, having a handler for outputs makes the switching between simulated and real hardware execution more seamless. It becomes cumbersome for developers to switch between simulation and using real hardware when there are major software differences between both modes.

Applications Engineer

National Instruments