- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA timing far from promises

Solved!04-27-2016 10:25 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

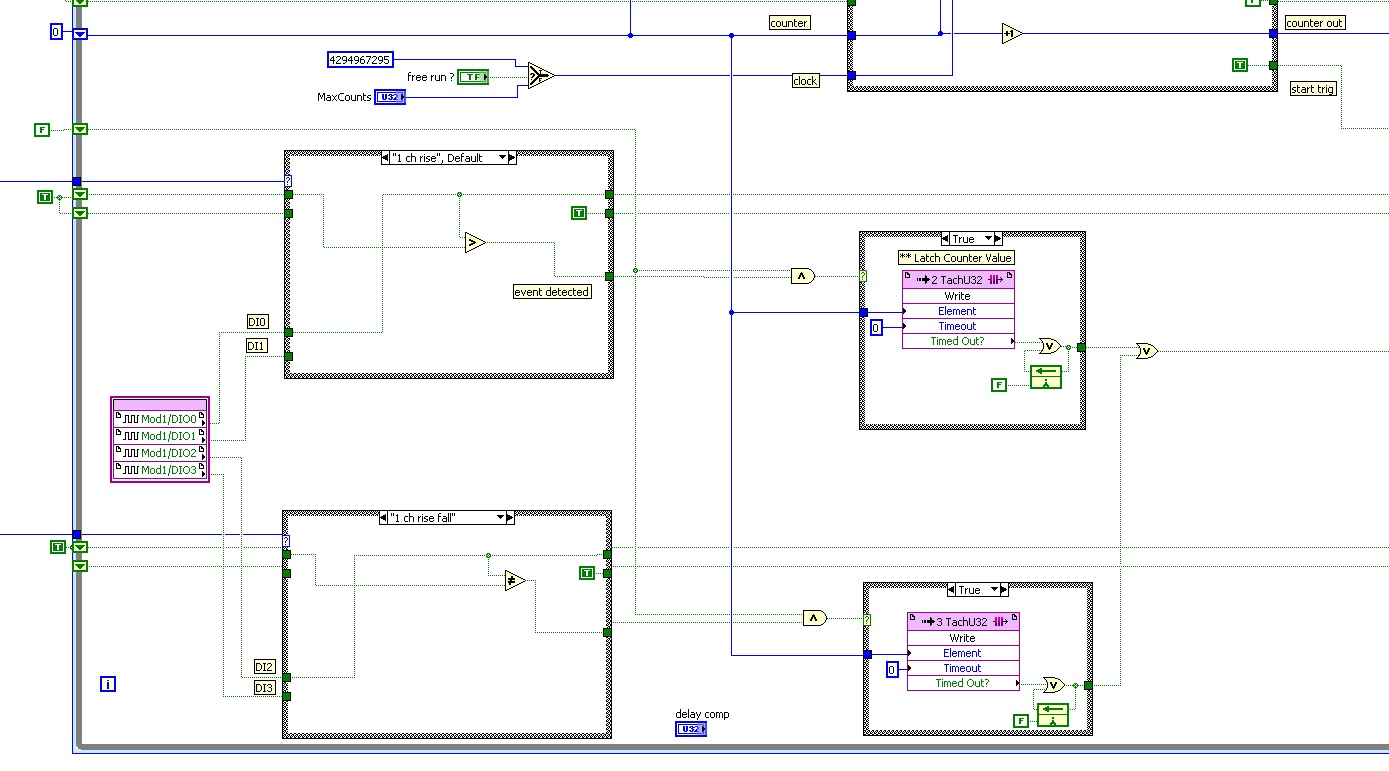

My application focus on measuring time between digital TTL events. The hardware used consist on cRIO9068 and high speed 9402 module. Since the hardware channel can run up to 16MHz and FPGA single loop can achieve 80MHz clock, I aspected to have for this application an accuracy around 5 ticks (1 ticks = 12.5ns = 1/80MHz, 5 ticks =62.5ns =1/16MHz).

Well i can test the application feeding squares to 9402 via a function generator (high quality one). While the accuracy on time regarding only rise (or only falling) TTL events is quite good (10 ticks at 1kHz ) once i use to deal with both rise and fall events the accuracy became around 60 ticks.

Who is guilty here ?

However from what i see the paper specifications for these hardaware are not meet

Solved! Go to Solution.

04-27-2016 11:43 AM - edited 04-27-2016 11:43 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Rozzilla,

Who is guilty here ?

Well, most times the problem exists between keyboard and chair 😄 (PEBKAC)

Do you mind to show your VI (and full FPGA project)?

Without any more information from your side we cannot help you with your problem…

04-27-2016 11:51 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

most time maybe not this since it so simple to manage, i cannot share the code since this is not arduino forum (even ....)

04-27-2016 11:57 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

04-27-2016 12:05 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

TWL ??

putting in strange words doesnt help.. im not a beginner.

04-27-2016 01:12 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

@rozzilla wrote:TWL ??

I think GerdW meant "Timed While Loop" although I haven't seen that abbreviation before (and I've been using LabVIEW FPGA for a long time).

We really do need to see your code, as well as the project file to see how you configured your top-level clock and any derived clocks, in order to provide any assistance.

I would discourage you from using comparison functions (such as greater than/less than) for comparing booleans. Use standard boolean logic (AND, OR, etc) instead.

04-27-2016 01:27 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

maybe i wasnt too detailed but offcourse the code is compiled (correctly) with a single cycle timed loop with a derived (x2) clock of 80Mhz. I tried all the code possibilities regarding rise and fall reckon with no better luck

04-27-2016 01:51 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

You marked the thread as solved - did you solve the problem, or did you mark it solved by accident?

If you have not in fact solved the problem, unfortunately there's nothing more we can do to debug the problem without more information about both your code and your goal. All programmers, no matter how good they are, make mistakes occasionally, so we cannot trust that your code is correct based only on your statement that it is. If it turns out that you are correct that it's the hardware at fault, unlikely as that may be, we'll still want to see your code to prove it.

04-27-2016 02:00 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

you know nathand i am pretty in a situation since i was payed to develop this product and so im not the owner of the code and for this i cant share it, from the other side i spent some of my time (it is not expensive, but not free as well) dealing with "calibration" of NI hardware. So right now i prefer to close this topic and shut up. hope you dont mind too much

thank you