- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA timing different in execution mode and simulation mode

01-20-2020 07:29 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

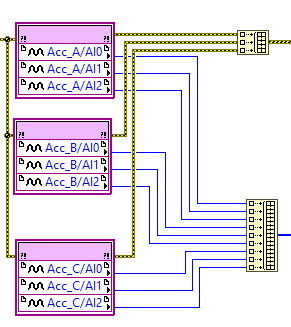

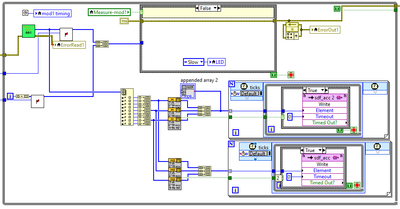

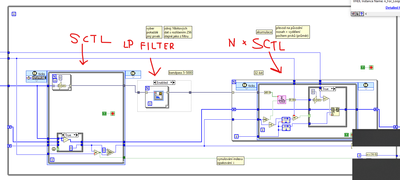

I use a while loop to read inputs of 3 x NI 9232 in cRIO 9057 @ 102400 Hz, which means 9 channels. I need to use a set of two filters on the FPGA and output in form of FIFO. The problem is that with more complex filter designs, the loop itself did not execute in time (10 μs), reading every one of two elements a halving the sampling rate. (10 μs is 400 ticks, sounds like a lot.) I used SCTL Single cycle timed loops where possible, but still have this issue.

And now to merit of the problem - when I compile and run the VI, my μs iteration timer VI shows 10 μs when working correctly and 20 μs if loop is not on time. When I do the same when in simulation, I get about 32 ticks (or 0 μs) per iteration. Isn't it supposed to reflect timing in execution mode?

This is how I read inputs (bright green VI):

This is the complete loop:

This is one of the filters (orange-grey VI):

Any ideas:

why it takes more than 10 μs to process the data?

why the simulation mode shows so much less time when on simulation?

how to improve the overall timing?

Thanks, Thomas

01-28-2020 01:31 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Any ideas? Maybe is my question unclear?

01-28-2020 02:03 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

01-28-2020 07:13 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

How do you then explain that the processing in execution mode takes about 10 times more? All the theoretical stuff concerning FPGA on NI website implies that the processing should take about 30 ticks - that's what simulation shows.

01-28-2020 08:01 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

01-28-2020 08:38 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you for your assistance! I don't think this is the answer to my question. I've read this article before and all it says that e.g. Wait VI set to 1000 ms on FPGA doesn't take 1000 ms to execute but probably less. But if i wrap the code in Tick Count VIs and measure the length of execution in ticks of FPGA, i should get the same result in simulation and in execution mode. Right? What would be the point if the timing was incomparable?

01-28-2020 08:47 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Thomas,

@Thomas444 wrote:

But if i wrap the code in Tick Count VIs and measure the length of execution in ticks of FPGA, i should get the same result in simulation and in execution mode. Right? What would be the point if the timing was incomparable?

No, you will not get the same amount of ticks as the simulation doesn't simulate "tick-accurate".

The point is: you can simulate your FPGA routines and check their calculations/output data before compiling, which can be a lengthy process…

01-29-2020 12:44 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Ok. I understand. Now could you please take a look at my code and try to tell from your experience what to improve in order to get under 10 μs (400 FPGA ticks) of processing time? Is there any obvious mistake in the code? Or is maybe the processing too complex for FPGA?

01-29-2020 12:53 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

01-29-2020 01:24 AM - edited 01-29-2020 01:30 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Ok here it is, version 17.0, I hope it is okay. 🙂

The content in the Disable structure is problematic - with content disabled, period in execution mode goes 10 μs and when enabled, it rises to 20 μs.