- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA: Set output state at boot (RT Linux)

06-14-2016 09:11 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Everybody.

Hardware: sbRIO-9607 (NI RT Linux, with Zynq-7020)

Software: LabVIEW 2015 SP1

How do I control the output state, when the target is rebooting, i.e. before the FPGA bitfile is loaded? I want my output state to be well-defined at all times.

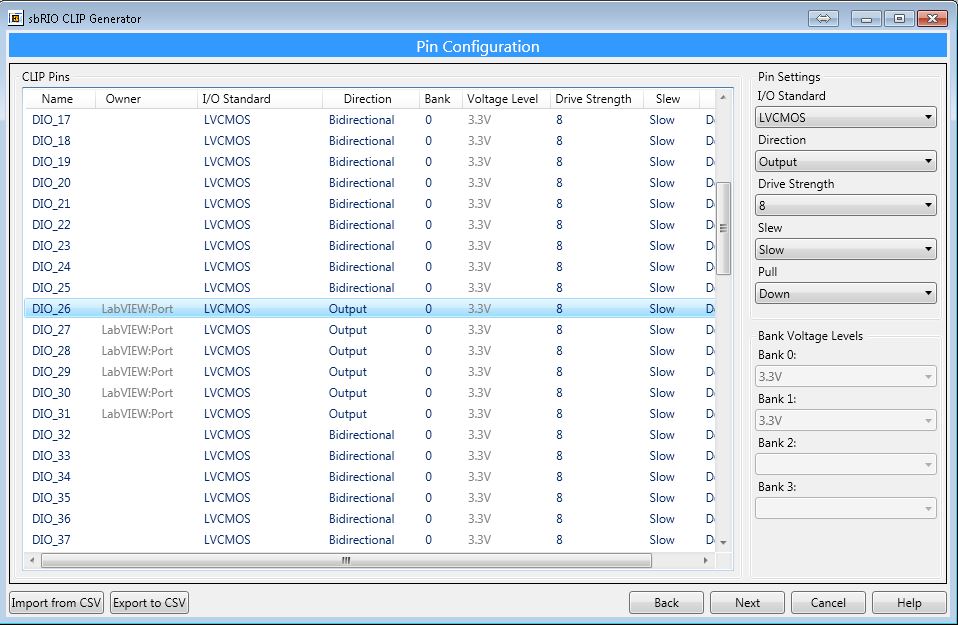

I have designed my own sbRIO CLIP, where I have defined my pins as output, and used a Pull-down implementation. But I guess that the pull-down only applies if you want to use the pin as an input? It feels like I’m missing the settings which controls the default state for outputs?

Alex E. Munkhaus

Certified LabVIEW Developer (CLD)

System Engineer

06-16-2016

02:49 AM

- last edited on

10-21-2025

04:41 PM

by

![]() Content Cleaner

Content Cleaner

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello,

I am Ed from National Instruments Applications Engineering. I have been forwarded your query with regards to controlling the FPGA I/O between restarts which is very intriguing indeed.

Primarily the answer is that this is not possible due to how the FPGA operates in relation to the controller However since you are using a Linux system you do have alot of control in terms of how the Operating System behaves.

What instances do you see that would require your real time application to restart or your controller to reboot?

If this is due to power loss I would recommend to have a UPS as a back up power supply in the event of power loss so that this does not occur.

If it is due to a requirement to for the real time executable to be restarted, you can use shell scripts to perform the restart instead in Linux as described in the below linked article:

https://knowledge.ni.com/KnowledgeArticleDetails?id=kA00Z000000P9uiSAC&l=en-US

It is also mentioned here that you can use pull-up and pull-down resistors for performing this action also. I have found also the article linked below along with the proceeding white paper which illustrate that you can use the RIO Device Setup to have the FPGA loaded from Flash independant of the host controller upon a restart. Then in your host controller you will need to modify the Open FPGA Reference VI to not run the FPGA VI (otherwise this will reinitialise the FPGA):

https://knowledge.ni.com/KnowledgeArticleDetails?id=kA00Z000000P9mASAS&l=en-US

https://www.ni.com/en/support/documentation/supplemental/09/managing-fpga-deployments.html

I hope that this provides you a solution which could be applicable to your application needs.

Best regards,

Ed