- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA STCL Multiple Clock Sources

Solved!07-08-2021 11:41 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello everyone,

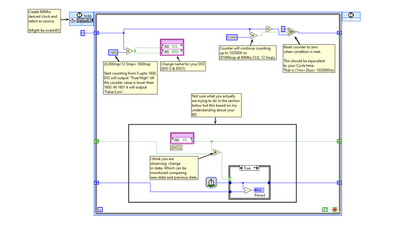

I have encountered some problems in using FPGA. My device is USB-7856R. I want to generate a trigger (gating signal), which lasts for about 20μs at a high level, and then stays at a low level until the next high level comes (100ms later). At the same time, I also need to detect the digital square signal (about 1MHz) obtained from DIO2. I use the counter method and use SCTL to select the 80MHz clock(because of accuracy and speed).

I want to put these two VIs into the same VI, but I am prompted to use multiple clock sources. Can you tell me what to do? Thank you very much.

Or is there another way to achieve digital trigger output?

Solved! Go to Solution.

07-09-2021 09:10 AM - edited 07-09-2021 09:11 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hi Clel,

I believe this is one way of achieving what you are trying to do. Do not consider this as a fact but from what I know you are putting IO nodes off the same connector and all the DIO on that connector would need the same clock to operate. Your clock in top while loop (Cycle time) will be different than the 80Mhz (12.5nsp) cycle time. I would suggest reading some articles about this to better understand. I did not have time look up one for you.

This is just to give an idea to approach what you are trying to do until someone comes up with a better answer. Hope this helps 😬

07-09-2021 10:43 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Thank you for your suggestion! I will try it!