- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FPGA Loop Time with Mean DC

06-27-2018 11:39 AM - edited 06-27-2018 11:40 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

06-29-2018 09:30 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report to a Moderator

Hello Peter,

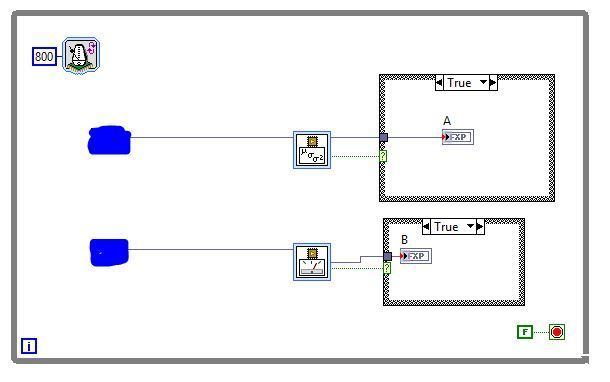

So from my understanding, if you're sampling at 40MHz, you'll be pulling in a sample every 2.5e-8 seconds. This means you'll get to 50 samples after 1.25us (1.25e-6).

I believe you'd need to set your while loop rate to the however many ticks needed to wait 25ns.

If you're gathering a single sample from these VIs every loop, I would check to see if you've gone through 50 loop iterations with an Equal? VI and have that boolean wired up to the stop terminal. Alternatively, you can just use a for loop with 50 iterations. Each loop will allow you to auto-index an output array.

Applications Engineer

National Instruments